Tutorial 2: BCD to 7 Segment FPGA Implementation

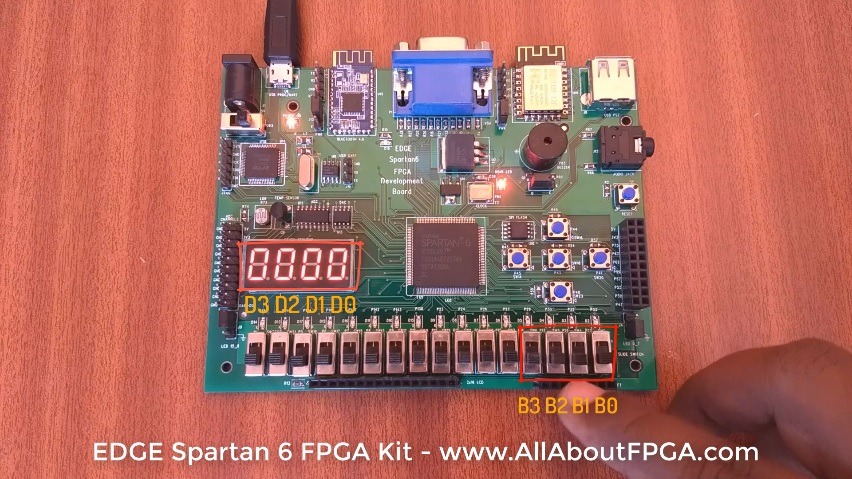

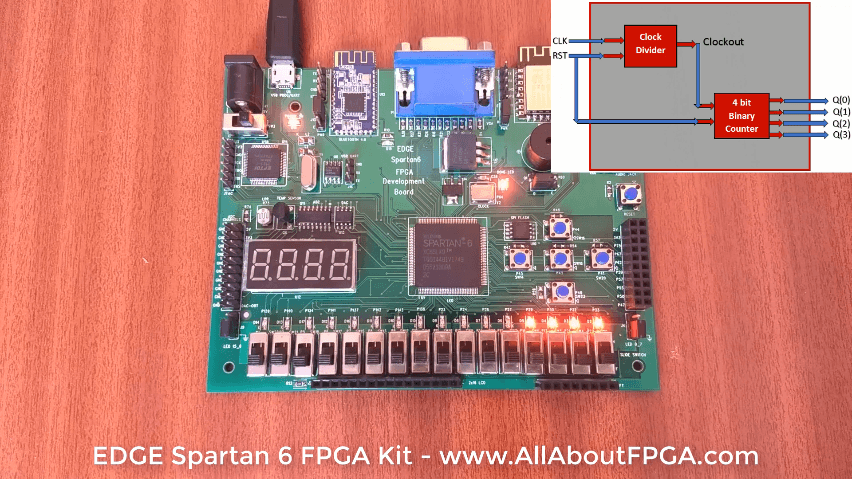

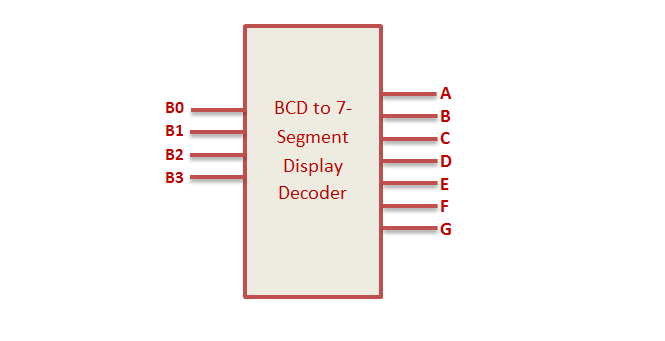

EDGE Spartan 6 FPGA Development Board consist of 16 No. of slide switches and 4 digit seven segment display. Lets display the 4 bit BCD of slide switches in the 4 digit seven segment display. 4 Digit 7 Segment Display present on edge board is common anode display. All 4 digits can be enabled by … Read more