Low Cost and Feature Packed FPGA Development Kit for Beginners.

Low Cost FPGA Kit to work with Latest Xilinx Vivado Design Suite.

Best Rated and All in One FPGA kit to work with Latest Xilinx Vivado Design Suite.

Feature rich and high-performance Single Board Computer

High-performance FPGA for Advanced Motor control Application

The ultimate FPGA kit for Academic Learning

EDGE FPGA kits contain onboard USB JTAG fully compatible with the Free version of Xilinx ISE / Vivado Design Tools, so designs can be implemented at no additional cost.

On-board USB Programmer

Iot Ready WiFi Connectivity

Bluetooth 4.0 BLE Ready

VGA/HDMI Display Port

ADC/DAC Converter

Camera/Display Interface

![]()

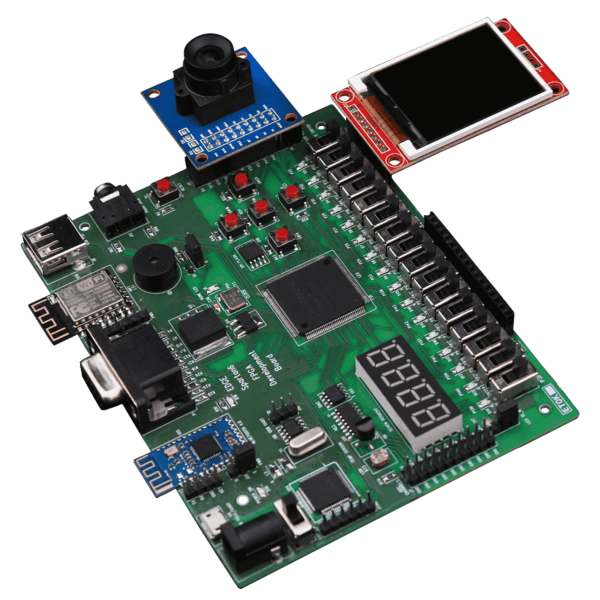

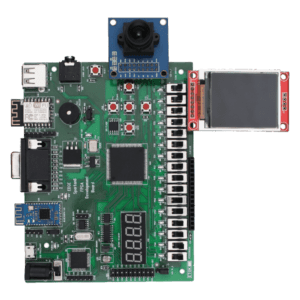

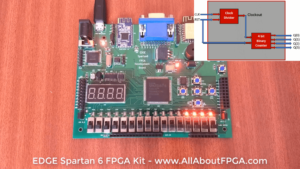

EDGE Spartan 6 FPGA Development board is the feature rich development board with Spartan 6 FPGA, SPI FLASH, ADC, DAC, LCD, 7 segment Display, WiFi, Bluetooth, Buzzer, Stereo Jack, Temperature Sensor and LDR. The Board also provides additional interface like CMOS Camera and TFT Display at the expansion connectors..

The EDGE Spartan 6 board is fully compatible with Xilinx ISE, EDK, System Generator and ChipscopePro Tools at ease with on-board USB JTAG Interface.

![]()

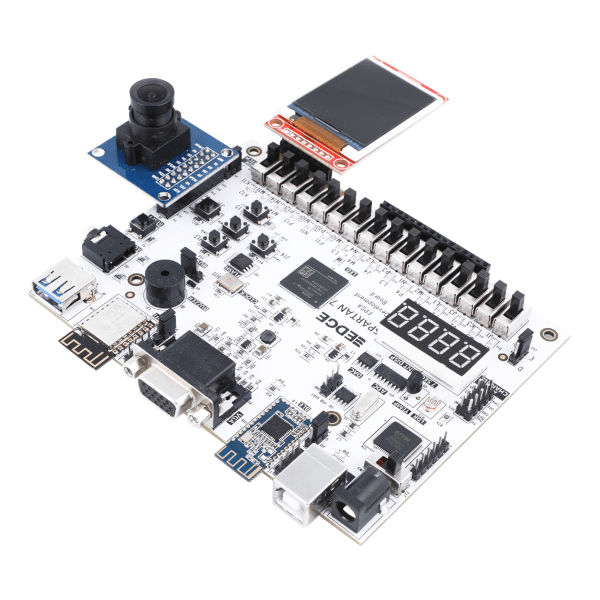

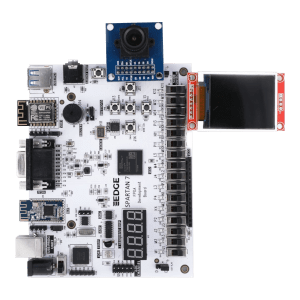

EDGE Spartan 7 FPGA kit is upgraded from EDGE Spartan 6 kit. Both EDGE Spartan 6 and Spartan 7 share the same interfaces except FPGA IC. An advantage of EDGE Spartan 7 over Spartan 6 is more logic resources and fully compatible with Vivado design suite.

Its features includes FPGA, SPI FLASH, Wi-Fi, Bluetooth, ADC, DAC, LCD, 7 segment, VGA, PS2, Stereo Jack, buzzer, Push Button, Slide Switch, LED, Temperature Sensor, LDR and UART.

![]()

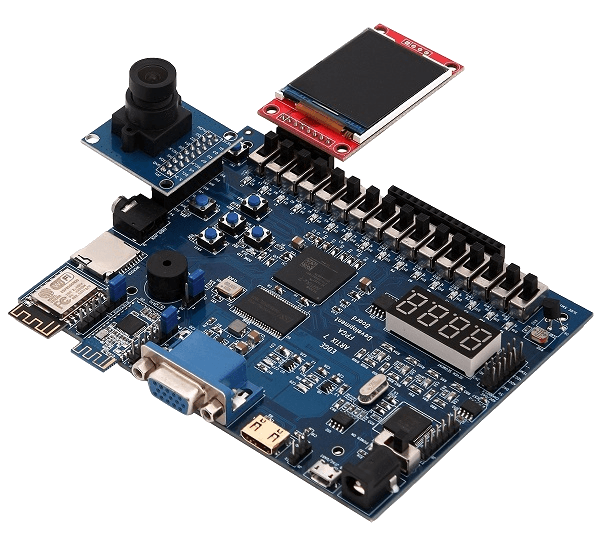

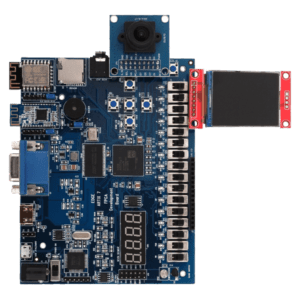

EDGE Artix 7 FPGA Development board is more powerful FPGA kit with plenty of on board interfaces. It is exclusively designed for the latest vivado Design Suite.

The EDGE Artix 7 board is build around Xilinx Artix 7 XC7A35T FPGA IC. The features includes external memory SDRAM, VGA, HDMI Out, Micro SD, WiFi, Bluetooth, ADC, Temperature Sensor, LDR, DAC, LCD, 7 Segment, camera, TFT, Buzzer, Switches, buttons and LEDs interface.

![]()

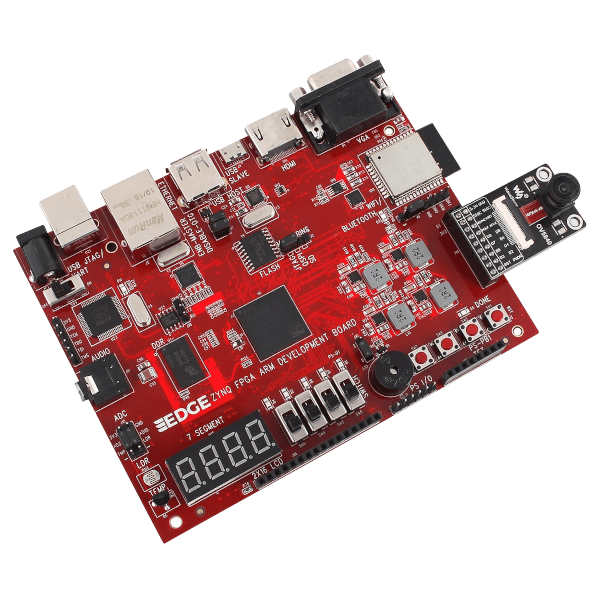

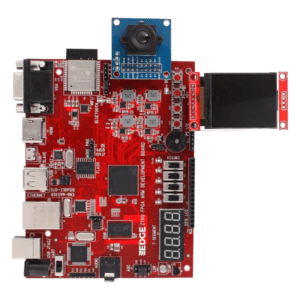

EDGE ZYNQ SoC FPGA Development Board is a feature rich and high-performance Single Board Computer built around the Xilinx Zynq Z7010/Z7020 FPGA. It features integrated dual-core ARM Cortex-A9 processor with Xilinx 7-series FPGA.

It features Xilinx ZYNQ SoC, 512MB DDR3 SDRAM and 16MB QSPI Flash USB-to-UART, USB OTG, Gigabit Ethernet, HDMI, USB JTAG, Micro SD, WiFi, Bluetooth, ADC, LCD, 7 Segment and lot more.

Madhur Juneja

EDGE Spartan 6 FPGA development board is an excellent kit for beginners like me. This provides feasibility approach to test our ideas as well. Because of the features included with kit.

Dr.Prakash

Build quality of the board is very good. The features provided are excellent for the price. Manuals are reasonably comprehensive, easy to follow for a beginner. An ideal way to explore the Xilinx Vivado software.

Leslie Ayling

Very Good Product for academicians to have an exposure on building SOC based solution and appreciate its capabilities. Support system and Training is very good from INVENT LOGICS.

Thanks.

Jyothi Bali

Excellent board for learning fpga and asic development. Very easy to connect and program this Artix7 board by laptop. There is no need of any external power supply and usb plateform cable. Documents and tutorials provided with kit is very helpful. After sell support and service is very quick and useful. All types of major peripheral and interfaces are provided on board. Highly recommended this Artix7 board.

Neeraj Kumar Yadav

BLOG POST

Learn FPGA: EDGE FPGA kits tutorial series

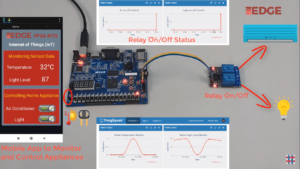

Remote Monitoring and control of Home appliances from cloud using EDGE Artix 7 FPGA board

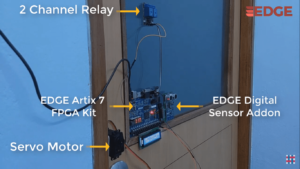

Social distancing with Gesture based door/light control using Edge Artix 7 FPGA board

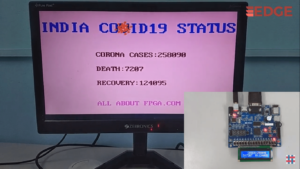

IoT Covid19 updates in 2×16 LCD and VGA Monitor using EDGE Artix 7 FPGA kit

Introduction and Advantages of Digital Sensor Addon for EDGE FPGA kit

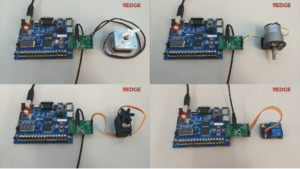

Introducing Motor Drive Addon for EDGE FPGA kit

FPGA Implementation of Internet of Things (IoT)

Tutorial 3: ALU Structural Modelling FPGA Implementation

Tutorial 2: BCD to 7 Segment FPGA Implementation

Tutorial 1: Binary Counter FPGA Implementation

OUR CLIENTS

Start FPGA learning with EDGE FPGA kits!