Table of Contents

What is FPGA?

Field-programmable gate array (FPGA) is a device that has array of Configurable logic gates and can be programmed on-board through dedicated Joint Test Action Group (JTAG) or through any other serial/ Parallel non-volatile Memory. FPGA architecture are based on static random-access memory (SRAM) Volatile memory. The Data programmed inside the memory of an FPGA erase once the board powered off. In order to configure the data, external EEPROM is attached to FPGA.

Any type of digital hardware circuit can be implemented in FPGA Architecture. The Configurable logic block can be used to design basic combinational logic circuit to complex Processor Architecture.

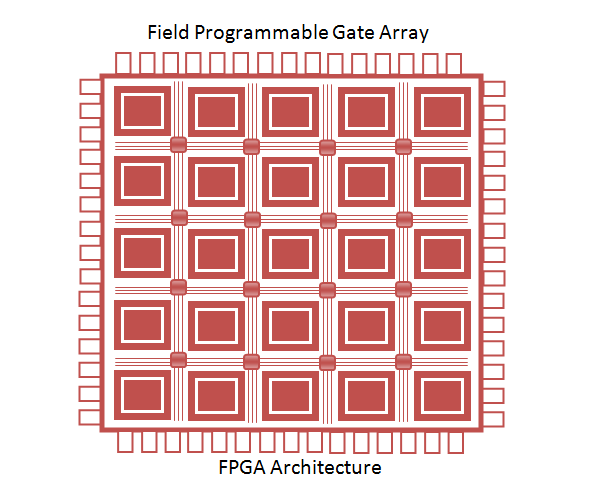

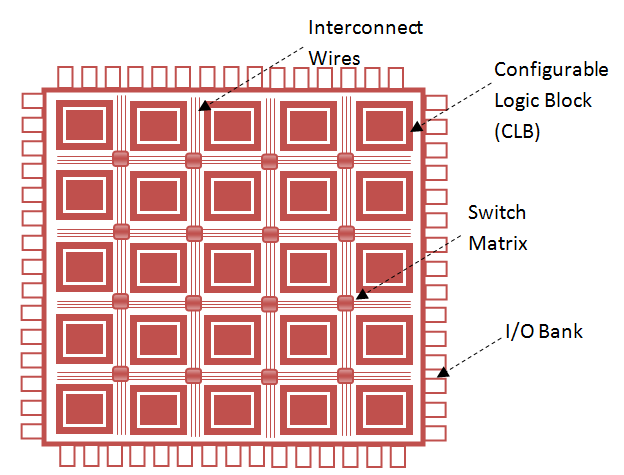

FPGA Architecture

FPGA architecture with Configurable logic Block CLB is shown in figure.

FPGAs, can be used to implement an entire System On one Chip (SOC). The FPGA has the advantage of re-programmable hardware architecture. In case of microprocessor it is not possible to implement re-configurable Hardware .

FPGA Architecture Features

FPGA Architecture consist of the following features

- Configurable logic Block (CLB)

- Input/Output Block

- Switching Matrix Interconnects

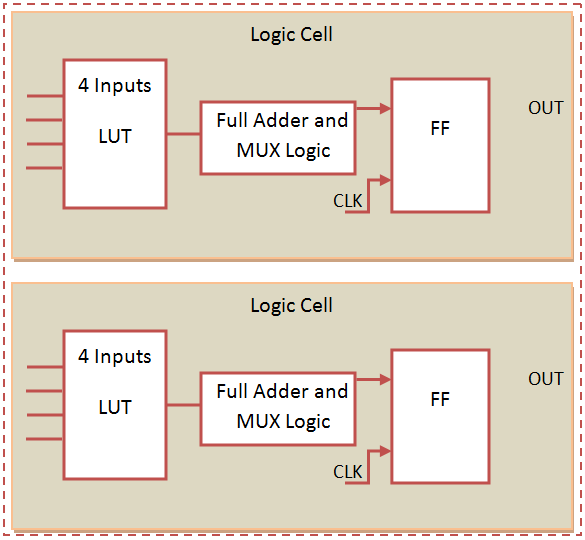

In FPGA, each Configurable Logic Block consist of 2 slices. Those slices are further divided in 2 logic elements.

Logic elements consist of

- 4 input lookup Table

- Full Adder and Mux logic

- D FlipFlop

Configurable Logic Block

4 input Lookup table LUT is used to implement one of the following functionality

- Combinational Logic design

- Distributed RAM

- Shift Register

Also there are various dedicated circuits are present inside FPGA. They are Digital Clock Manager, Multiplier, Block RAM and so on.

Digital Clock Manager DCM is used to perform Clock Phase shift, De skew, Clock divider and frequency synthesis.

Multiplier Block implement dedicated 18×18 multiplier with Signed and unsigned operation.

Block RAM is a dedicated memory implement dual port 16kb memory.

In advanced FPGA Architecture like zynq FPGA from xilinx, dual core arm cortex A9 Processor is inbuilt inside the FPGA Fabric for high Performance implementation.