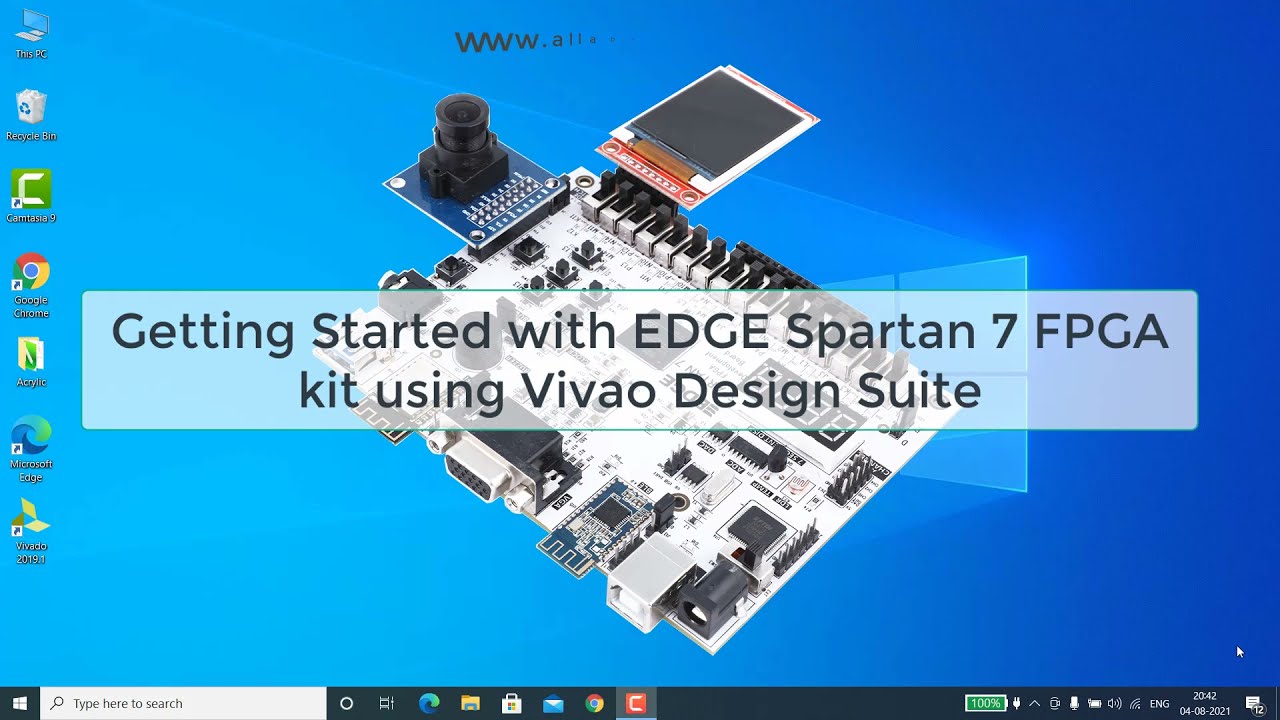

Learn FPGA: EDGE FPGA kits tutorial series

By Support Team

/

This tutorial series consists of learning VHDL programming with vivado design suite using EDGE Spartan 7 FPGA kit and EDGE...

Read More

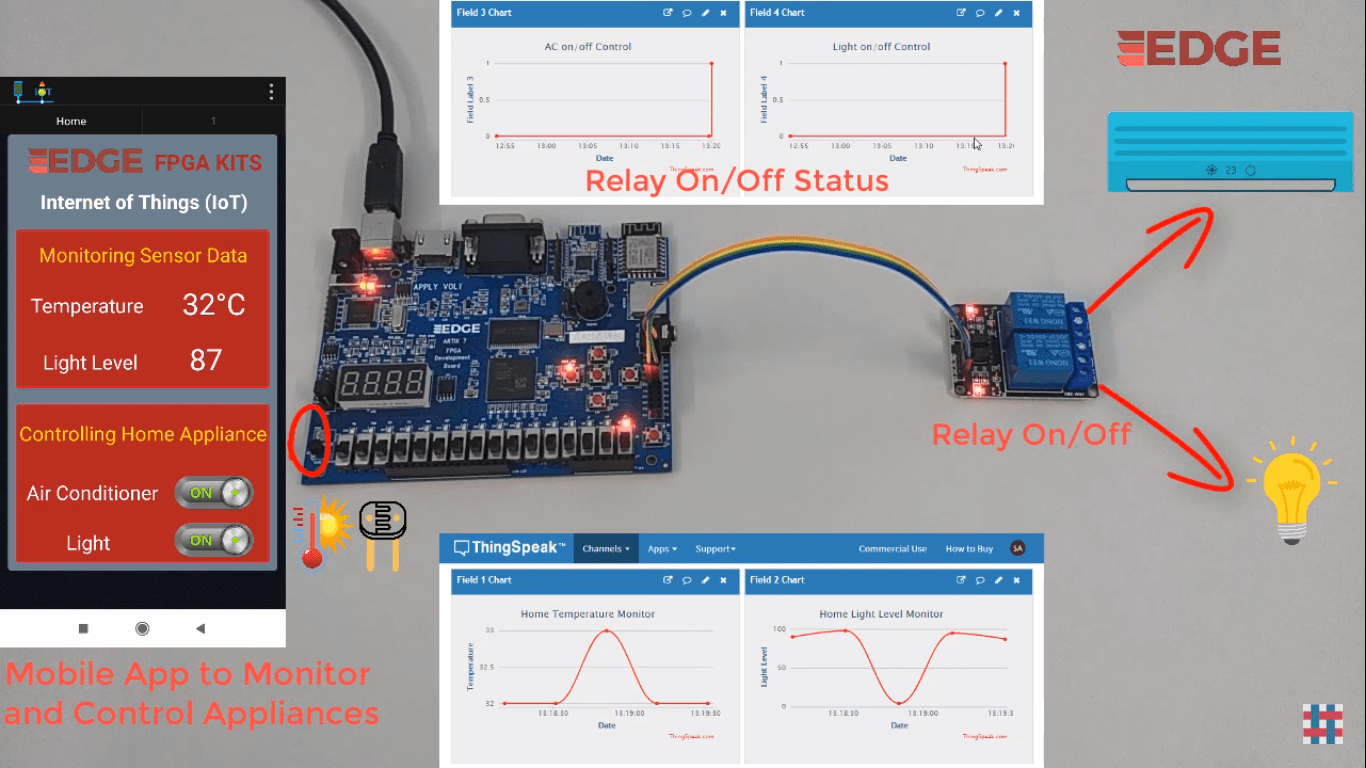

Remote Monitoring and control of Home appliances from cloud using EDGE Artix 7 FPGA board

By Support Team

/

In this IoT project, we are Monitoring Temperature, Light Intensity and control the home appliances such as air conditioner and...

Read More

1 Reply

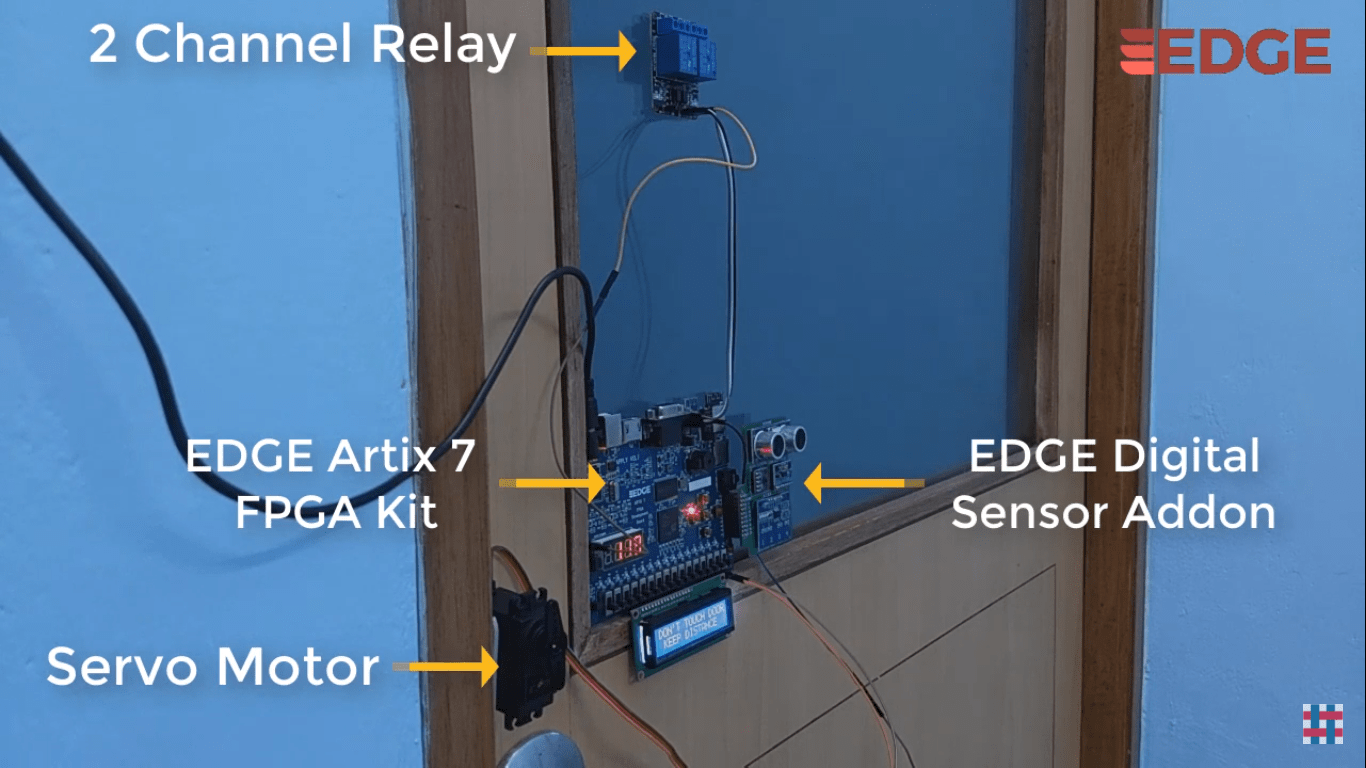

Social distancing with Gesture based door/light control using Edge Artix 7 FPGA board

By Support Team

/

In this project, we have implemented the hand gesture based Door open/close and Light on/off system using Edge Artix 7...

Read More

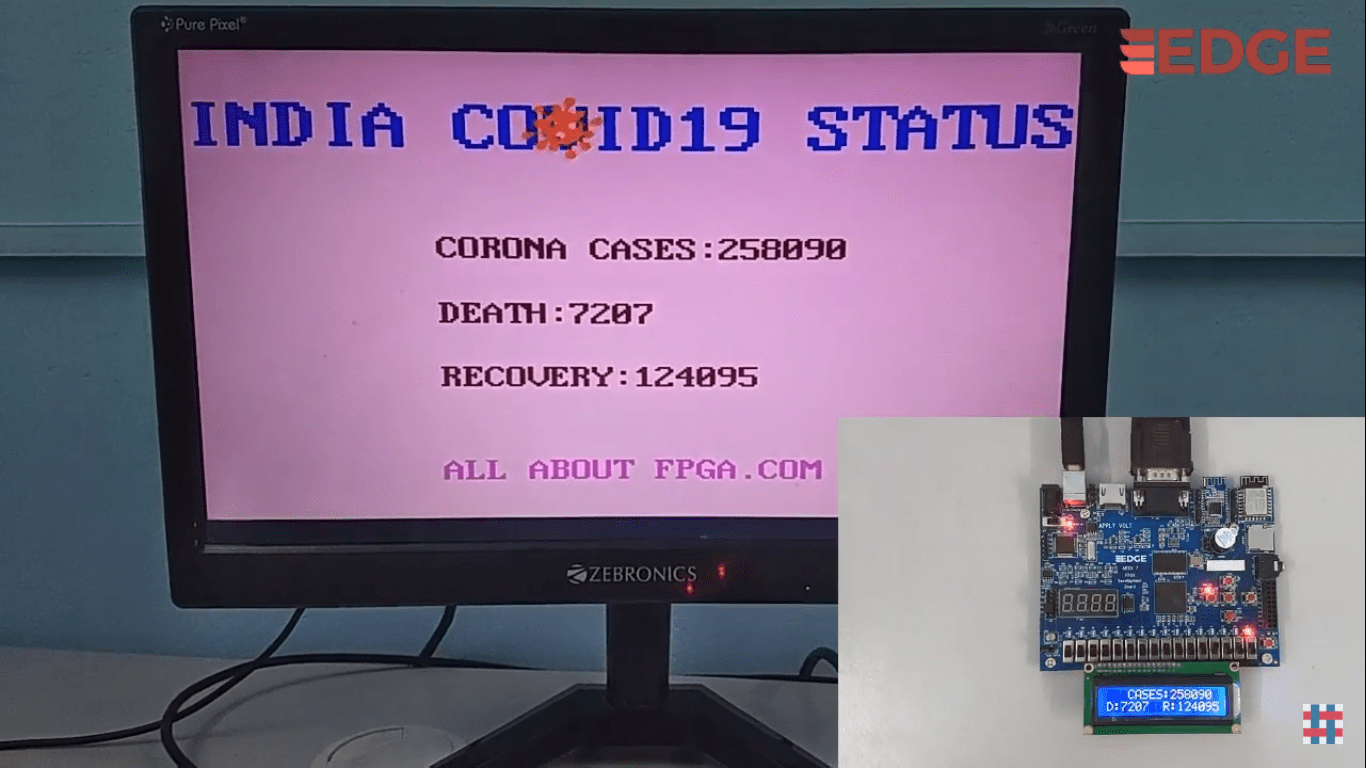

IoT Covid19 updates in 2×16 LCD and VGA Monitor using EDGE Artix 7 FPGA kit

By Support Team

/

This project visualizes the current data of the coronavirus outbreak of India in real-time on a VGA monitor and also...

Read More

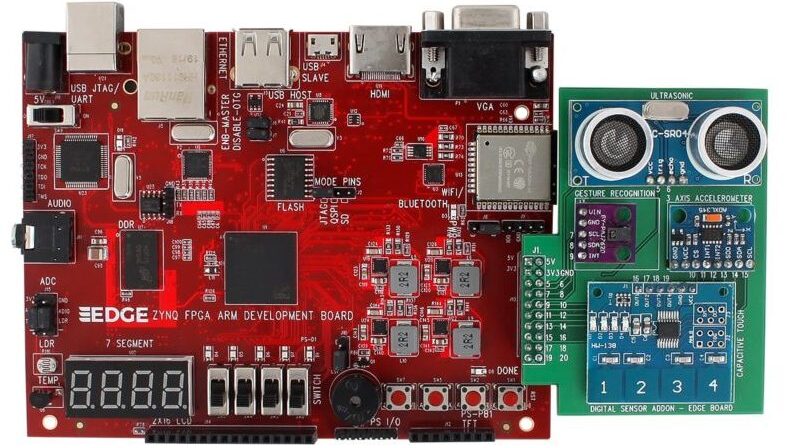

Introduction and Advantages of Digital Sensor Addon for EDGE FPGA kit

By Support Team

/

Digital Sensor Addon card is designed to interface 4 digital sensor modules to EDGE FPGA kits. Those sensor includes 3...

Read More

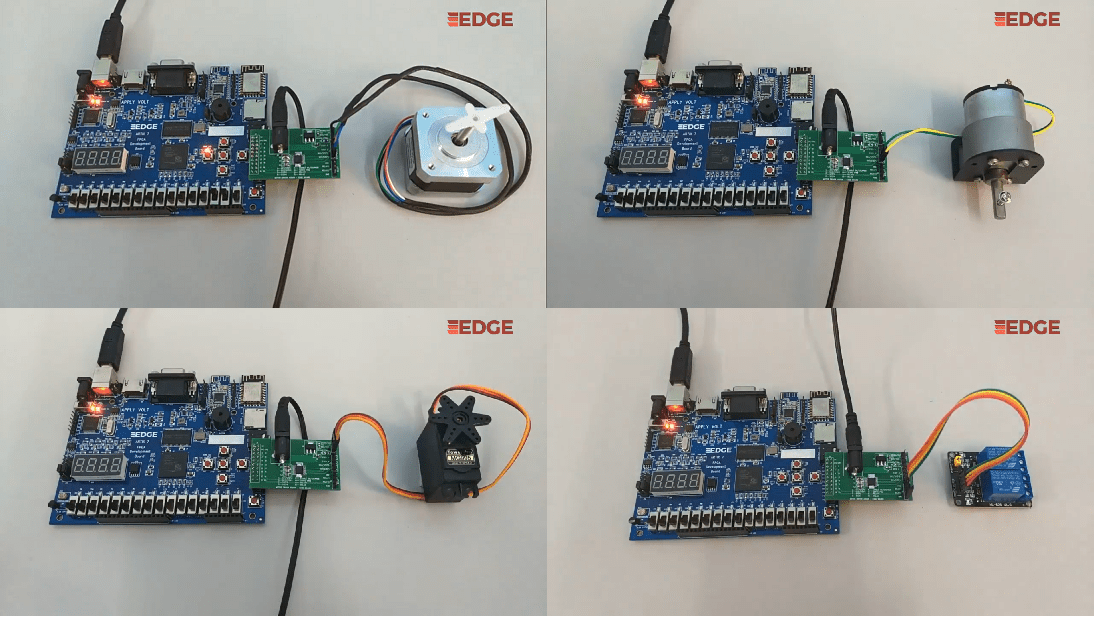

Introducing Motor Drive Addon for EDGE FPGA kit

By Support Team

/

Invent Logics bring you the motor driver interface card with motors and relay module. This motor driver can be directly...

Read More

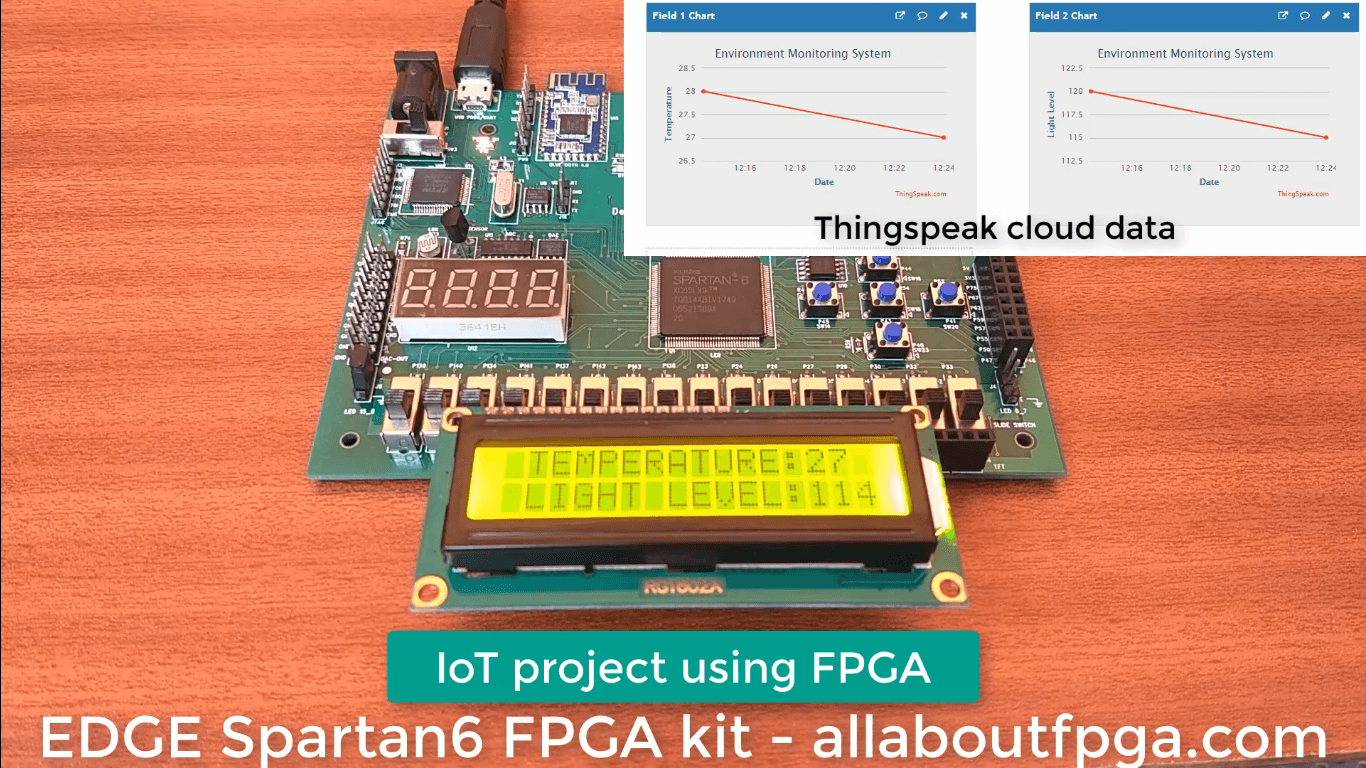

FPGA Implementation of Internet of Things (IoT)

By Support Team

/

Internet of Things IoT is the way of connecting physical objects with IP address to the cloud or any other...

Read More

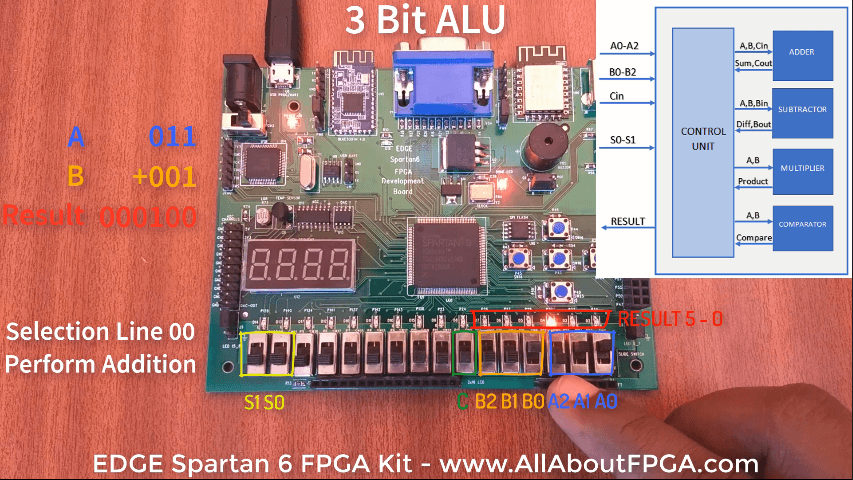

Tutorial 3: ALU Structural Modelling FPGA Implementation

By Support Team

/

ALU ALU internally always do multiple operations like addition, subtraction, division and multiplication. We have to specify which result you...

Read More

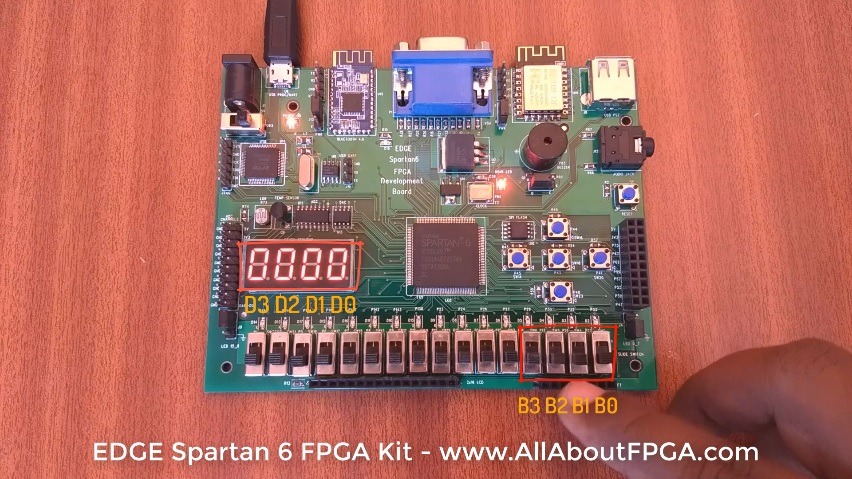

Tutorial 2: BCD to 7 Segment FPGA Implementation

By Support Team

/

EDGE Spartan 6 FPGA Development Board consist of 16 No. of slide switches and 4 digit seven segment display. Lets...

Read More

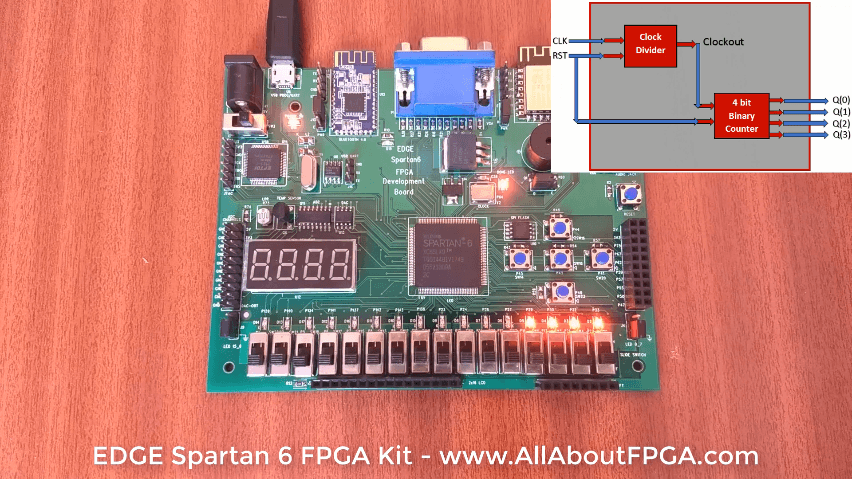

Tutorial 1: Binary Counter FPGA Implementation

By Support Team

/

In this tutorial, We implemented 4 bit binary counter using EDGE Spartan 6 FPGA Kit. It counts at every 0.5...

Read More

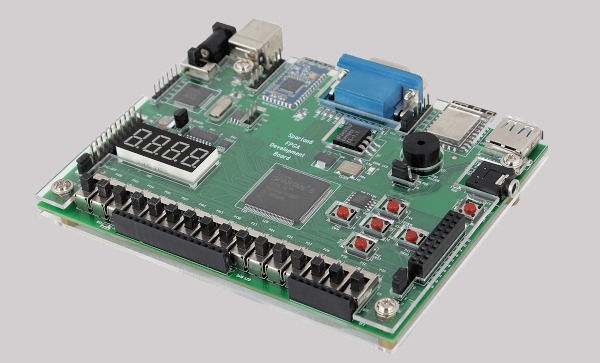

Introducing EDGE Spartan 6 FPGA Development Board!

By Support Team

/

All About FPGA brings you a feature rich development board for FPGA learners community. EDGE Spartan 6 FPGA Development board...

Read More

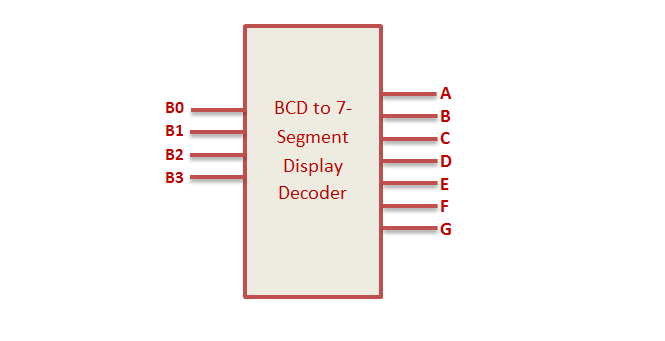

BCD to 7 Segment Decoder VHDL Code

By Support Team

/

VHDL Code BCD to 7 Segment Display decoder can be implemented in 2 ways. By simplifying Boolean expression to implement structural design and behavioral design.

For constructing BCD to 7 segment display, first construct truth table and simplify them to Boolean expression using K Map and finally build the combinational circuit.

Read More

Sequence Detector using Mealy and Moore State Machine VHDL Codes

By Support Team

/

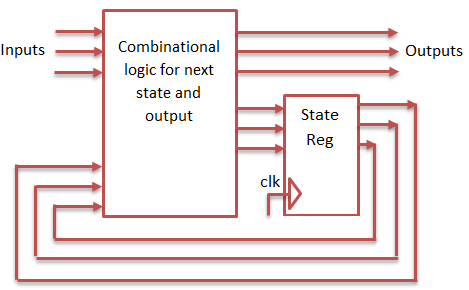

Mealy State Machine

The Output of the state machine depends on both present state and current input. When the input changes,the output of the state machine updated without waiting for change in clock input.

Moore State Machine

The Output of the State machine depends only on present state. The output of state machine are only updated at the clock edge.

Read More

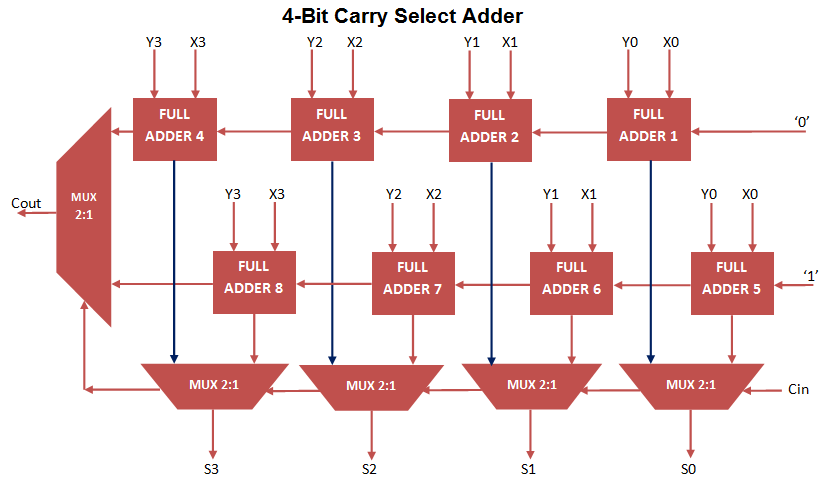

Carry Select Adder VHDL Code

By Support Team

/

Carry Select Adder VHDL Code can be Constructed by implementing 2 stage Ripple Carry Adder and multiplexer circuit. Carry Select Adder select the sum and carry output from stage 1 ripple carry adder when carry input '0' and select Sum and carry output from stage 2 ripple carry adder, when carry input '1'.

Read More

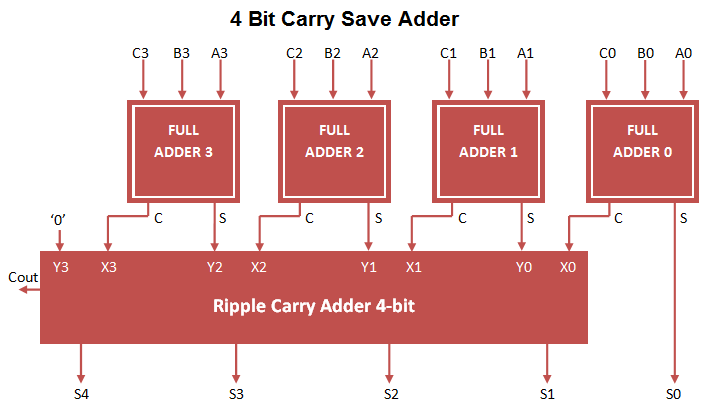

Carry Save Adder VHDL Code

By Support Team

/

Carry save adder used to perform 3 bit addition at once. Here 3 bit input (A, B, C) is processed and converted to 2 bit output (S, C) at first stage. At first stage result carry is not propagated through addition operation. In order to generate carry, implemented ripple carry adder on stage 2 for carry propagation. Carry Save adder VHDL Code can be constructed by port mapping full adder VHDL Code to 2 stage adder circuit.

Read More

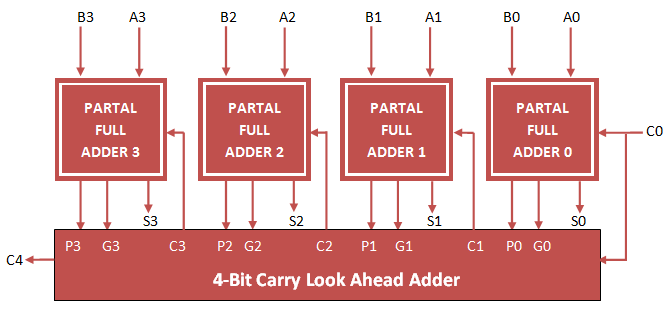

Carry Look Ahead Adder VHDL Code

By Support Team

/

Carry Look Ahead Adder is fastest adder compared Ripple carry Adder. For the Purpose of carry Propagation, Carry look Ahead Adder construct Partial Full Adder, Propagation and generation Carry block. It avoid Carry propagation through each adder.

In order to implement Carry Look Ahead Adder, first implement Partial Full Adder and then Carry logic using Propagation and generation Block.

Read More

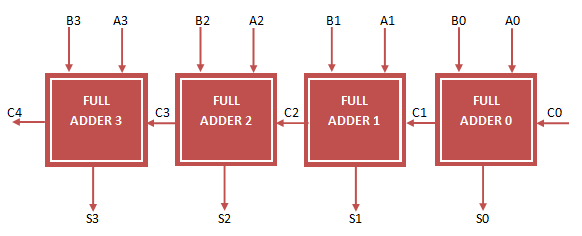

4 Bit Ripple Carry Adder VHDL Code

By Support Team

/

Ripple Carry Adder adds 2 n-bit number plus carry input and gives n-bit sum and a carry output. The Main operation of Ripple Carry Adder is it ripple the each carry output to carry input of next single bit addition. Each single bit addition is performed with full Adder operation (A, B, Cin) input and (Sum, Cout) output. The 4-bit Ripple Carry Adder VHDL Code can be Easily Constructed by Port Mapping 4 Full Adder. The following figure represent the 4-bit ripple carry adder.

Read More

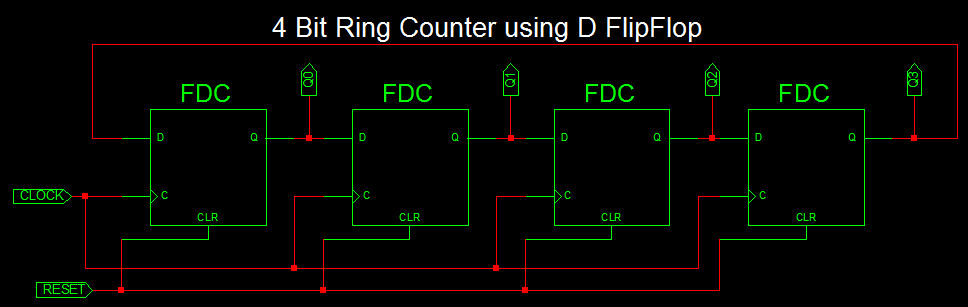

VHDL Code for 4-bit Ring Counter and Johnson Counter

By Support Team

/

Ring Counter very similar to shift register. At each clock pulse, data at each flipflop shifted to next flipflop with last output is feed back to the input of first flipflop. Also the first flop is set to '1' at the reset state. so it shift bit '1' to next flipflop for each clock input and repeat the sequence as shown below.

Read More

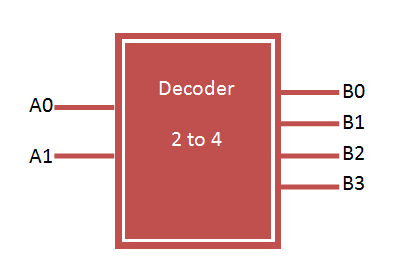

VHDL Code for 2 to 4 decoder

By Support Team

/

Binary decoder has n-bit input lines and 2 power n output lines. It can be 2-to-4, 3-to-8 and 4-to-16 line configurations. Binary decoder can be easily constructed using basic logic gates. VHDL Code of 2 to 4 decoder can be easily implemented with structural and behavioral modelling.

Read More

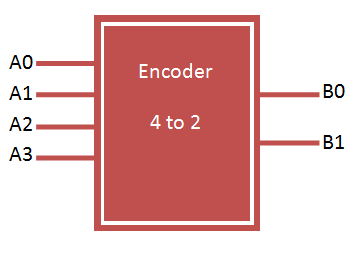

VHDL Code for 4 to 2 Encoder

By Support Team

/

Binary encoder has 2n input lines and n-bit output lines. It can be 4-to-2, 8-to-3 and 16-to-4 line configurations. VHDL Code for 4 to 2 encoder can be designed both in structural and behavioral modelling.

Read More

-

EDGE ZYNQ SoC FPGA Development Board₹ 17,500

EDGE ZYNQ SoC FPGA Development Board₹ 17,500 -

EDGE Artix 7 FPGA Development Board₹ 13,750

EDGE Artix 7 FPGA Development Board₹ 13,750 -

EDGE Spartan 6 FPGA Development Board₹ 8,500

EDGE Spartan 6 FPGA Development Board₹ 8,500