Reset Circuit helps to keep the FPGA in to Known State. There are 2 types Resets commonly employed to Reset FPGA. They are Asynchronous and Synchronous Reset.

Table of Contents

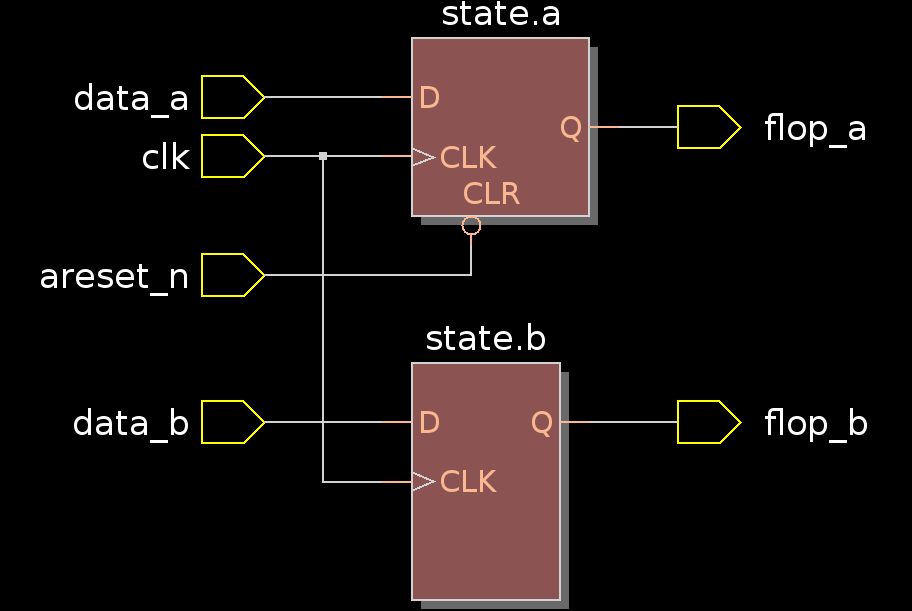

Asynchronous Reset

Asynchronous Reset circuit is independent of free running clock. Which means Reset circuit got no knowledge of Clock input. It can assert and desert a flipflop asynchronously.

VHDL Code for Asynchronous Reset

Library ieee;

use ieee.std_logic_1164.all;

entity asynchronous_reset is

port(clock, Reset, data: Std_logic;

q: srd_logic);

end asynchronous_reset;

architecture bhv of asynchronous_reset is

begin

process(clock,Reset,data)

if Reset = '1' then

q <= '0';

elsif Rising_edge(clock) then

q <= data;

end if;

end process;

end bhv;

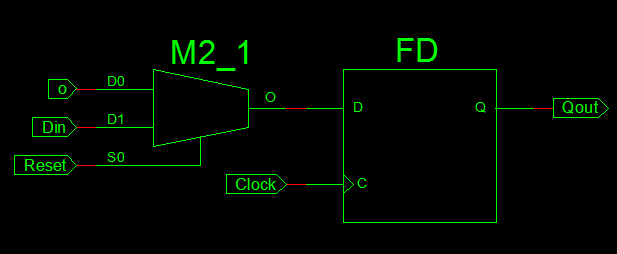

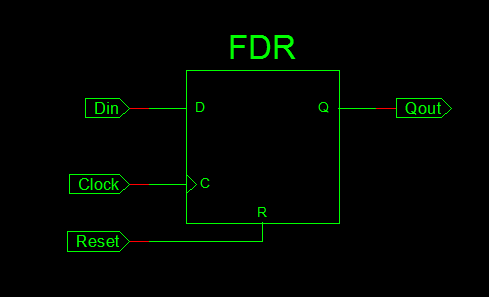

Synchronous Reset

Synchronous Reset circuit is always dependent on clock pulse input. It can assert and desert a flipflop synchronously.

VHDL Code for Synchronous Reset

Library ieee;

use ieee.std_logic_1164.all;

entity synchronous_reset is

port(clock, Reset, data: Std_logic;

q: std_logic);

end synchronous_reset;

architecture bhv of synchronous_reset is

begin

process(clock,Reset,data)

if Rising_edge(clock) then

if Reset = '0' then

q <= '0';

else

q <= data;

end if;

end if;

end process;

end bhv;

The sensitivity lists in your codes are incorrect.

For both codes, the data signal should not appear in the sensitivity list because we don’t care if it changes or not as long as the clock does not change.

For the synchronous reset code, the reset should not appear in the sensitivity list for the same reason.