Learn FPGA: EDGE FPGA kits tutorial series

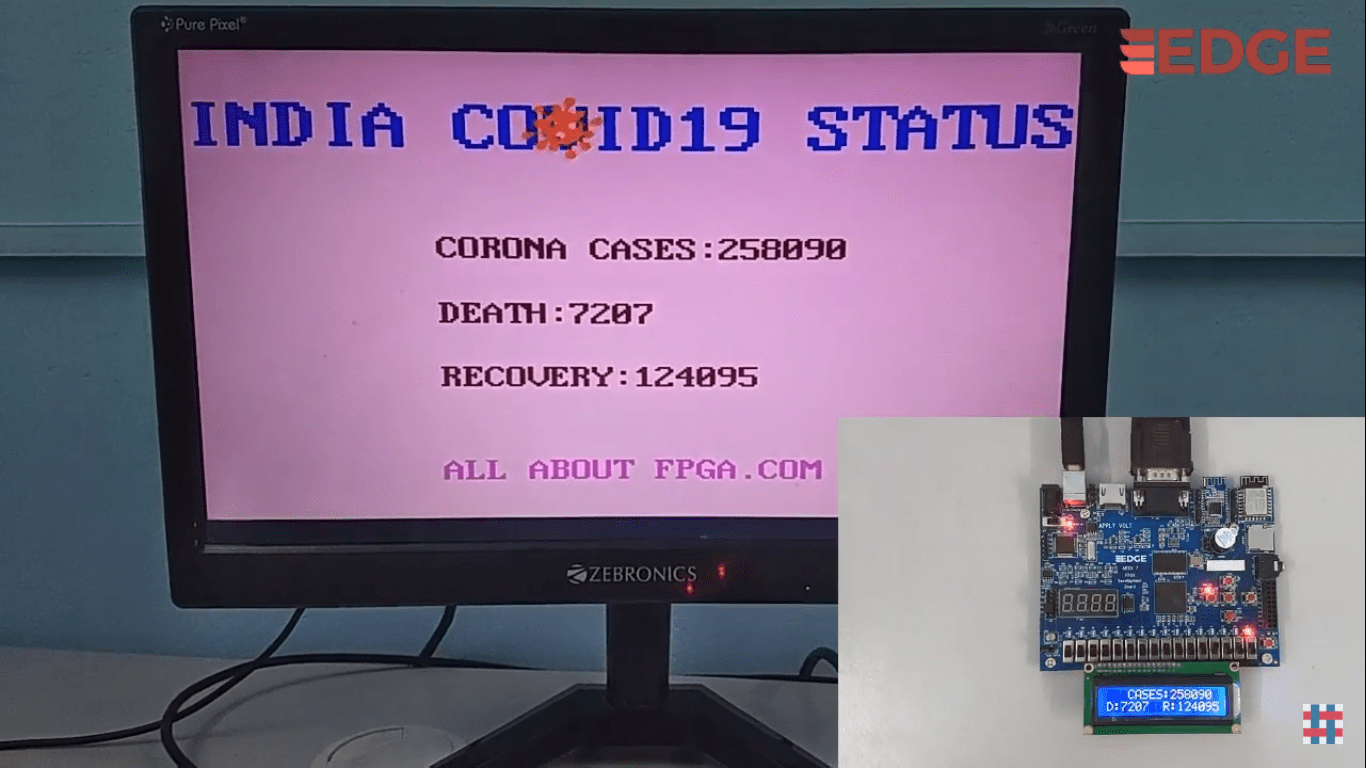

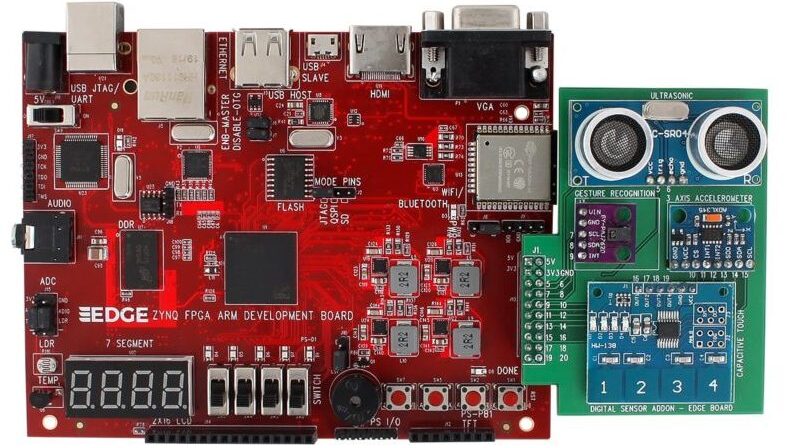

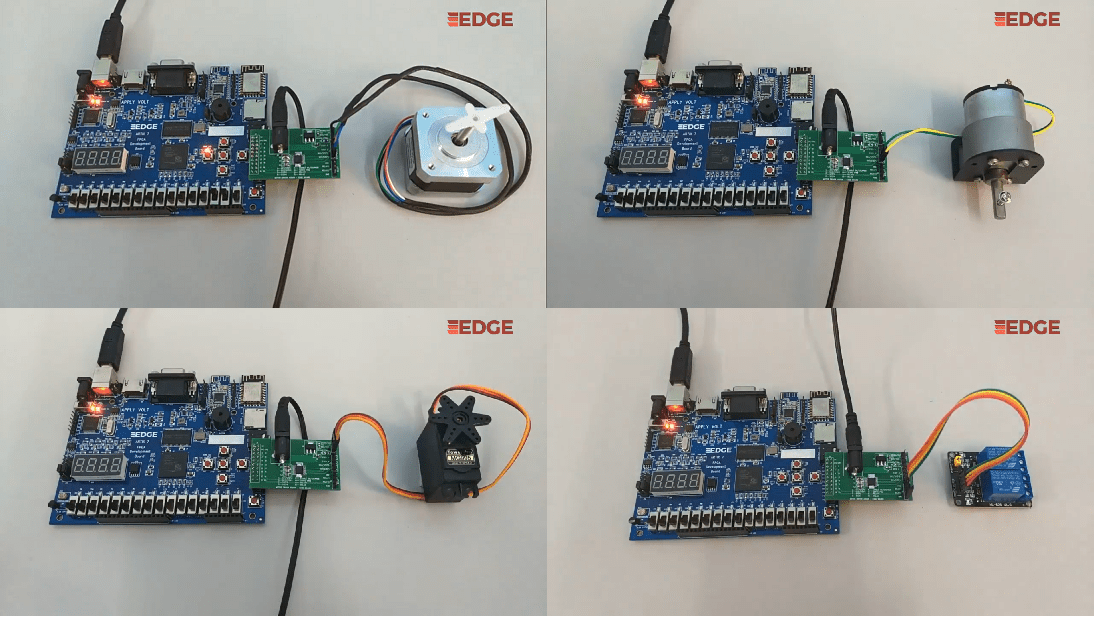

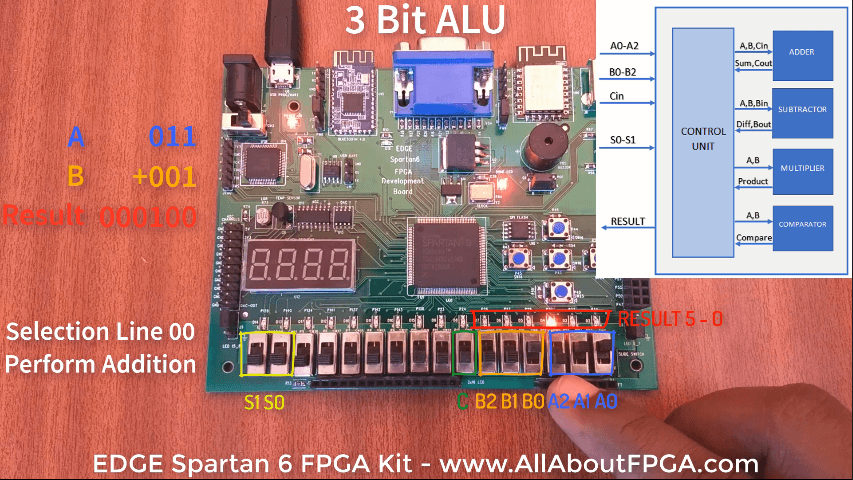

This tutorial series consists of learning VHDL programming with vivado design suite using EDGE Spartan 7 FPGA kit and EDGE Artix 7 FPGA kit. Getting Started with edge spartan 7 FPGA kit using Vivado Design Suite 4-bit Adder implementation using Half Adder and Full Adder on EDGE Spartan 7 FPGA kit 4×4 Multiplier implemented using … Read more