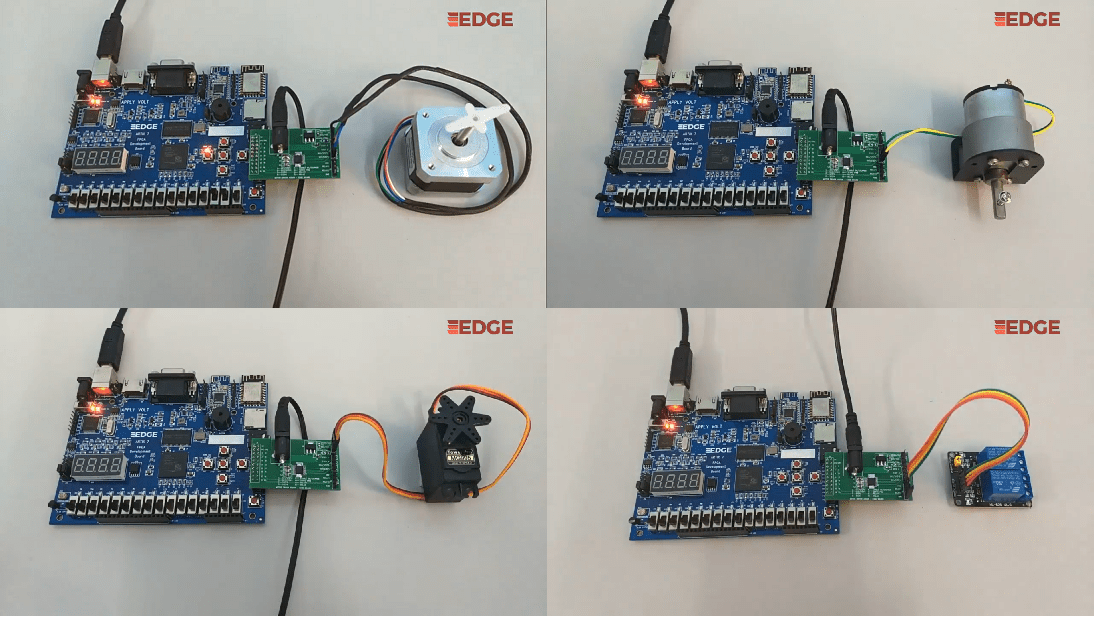

Introducing Motor Drive Addon for EDGE FPGA kit

Invent Logics bring you the motor driver interface card with motors and relay module. This motor driver can be directly connected with EDGE FPGA kits via 2×10 pin female header available on all the EDGE FPGA kits Motor driver interface card is designed with Texas Instruments motor control driver IC. Addon cards comes along with … Read more