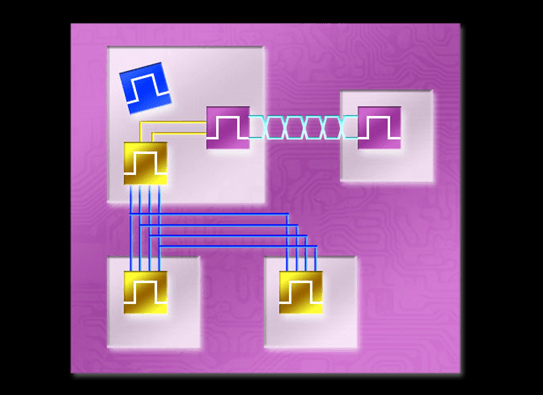

Digital Clock manager DCM in Xilinx FPGA

DCM provides clocking to all the resources of Xilinx FPGA with advanced feature. Digital Clock Manager DCM integrates advanced clocking capabilities to FPGA global clock distribution network.

It eliminates clock deskewing, Phase shifting, and also act as frequency synthesizer multiply/divide input clock.