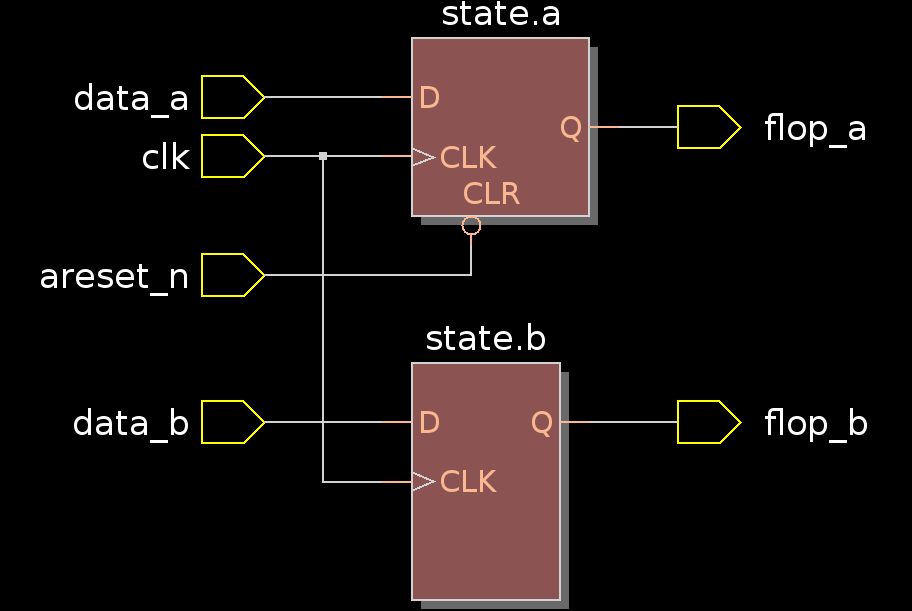

Synchronous and Asynchronous Reset VHDL

Reset Circuit helps to keep the FPGA in to Known State. There are 2 types Resets commonly employed to Reset FPGA. They are Asynchronous and Synchronous Reset.

Asynchronous Reset

Asynchronous Reset circuit is independent of free running clock. Which means Reset circuit got no knowledge of Clock input. It can assert and desert a flipflop asynchronously.