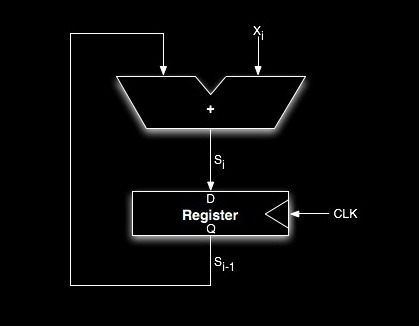

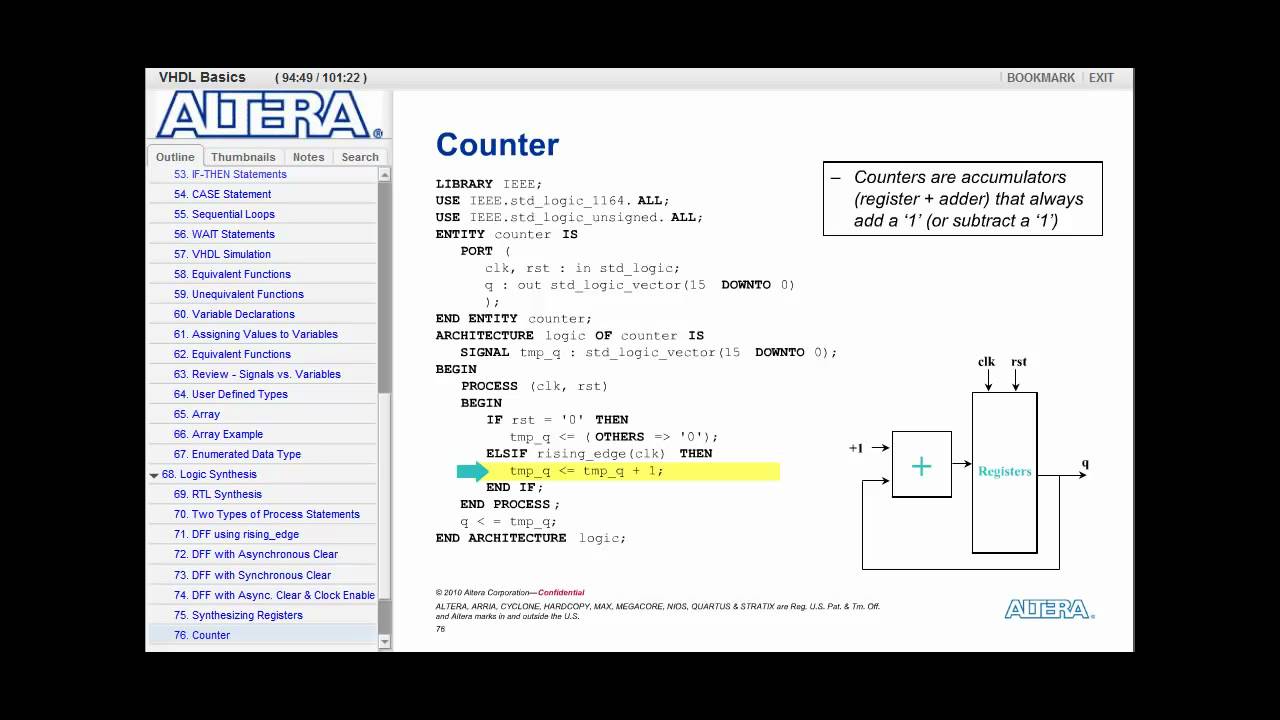

VHDL Code for 4-Bit Aynchronous Accumulator

By Support Team

/

Accumulator work similar to the functionality of counter. The main difference is instead increment the counter value by constant, Accumulator add the input value with the current value.

Read More

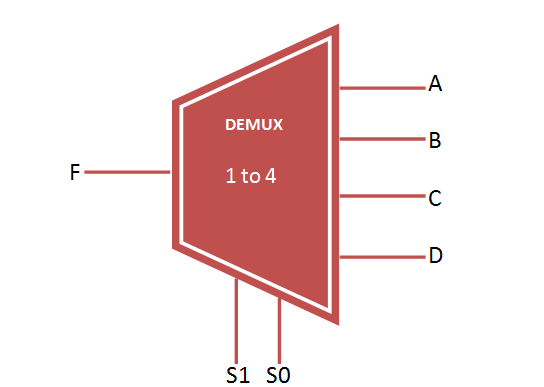

VHDL code for 1 to 4 Demux

By Support Team

/

Demultiplexer (DEMUX) select one output from the multiple output line and fetch the single input through selection line. It consist of 1 input and 2 power n output. The output data lines are controlled by n selection lines. For Example, if n = 2 then the demux will be of 1 to 4 mux with 1 input, 2 selection line and 4 output as shown below. Also VHDL Code for 1 to 4 Demux described below.

Read More

5 Replies

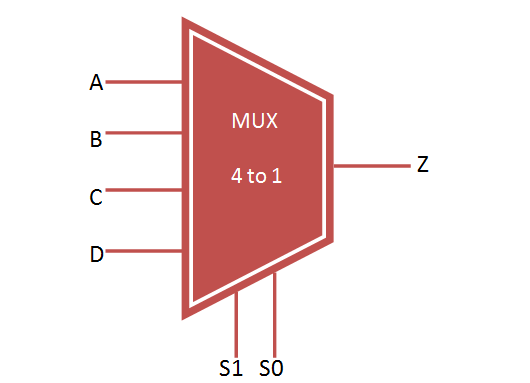

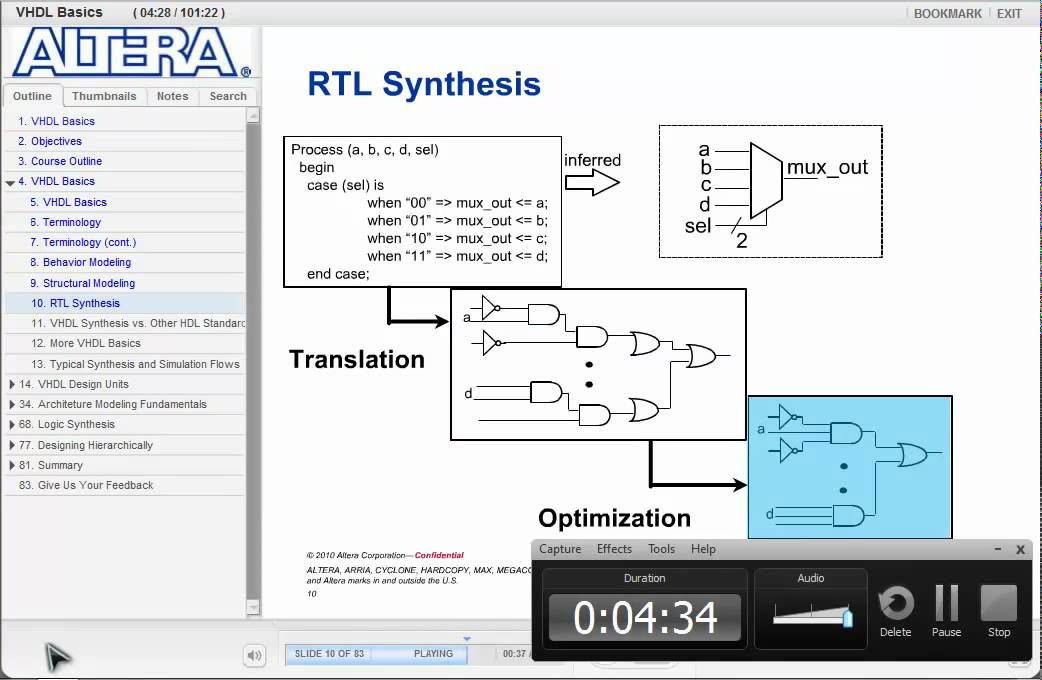

VHDL 4 to 1 Mux (Multiplexer)

By Support Team

/

Multiplexer (MUX) select one input from the multiple inputs and forwarded to output line through selection line. It consist of 2 power n input and 1 output. The input data lines are controlled by n selection lines.

Read More

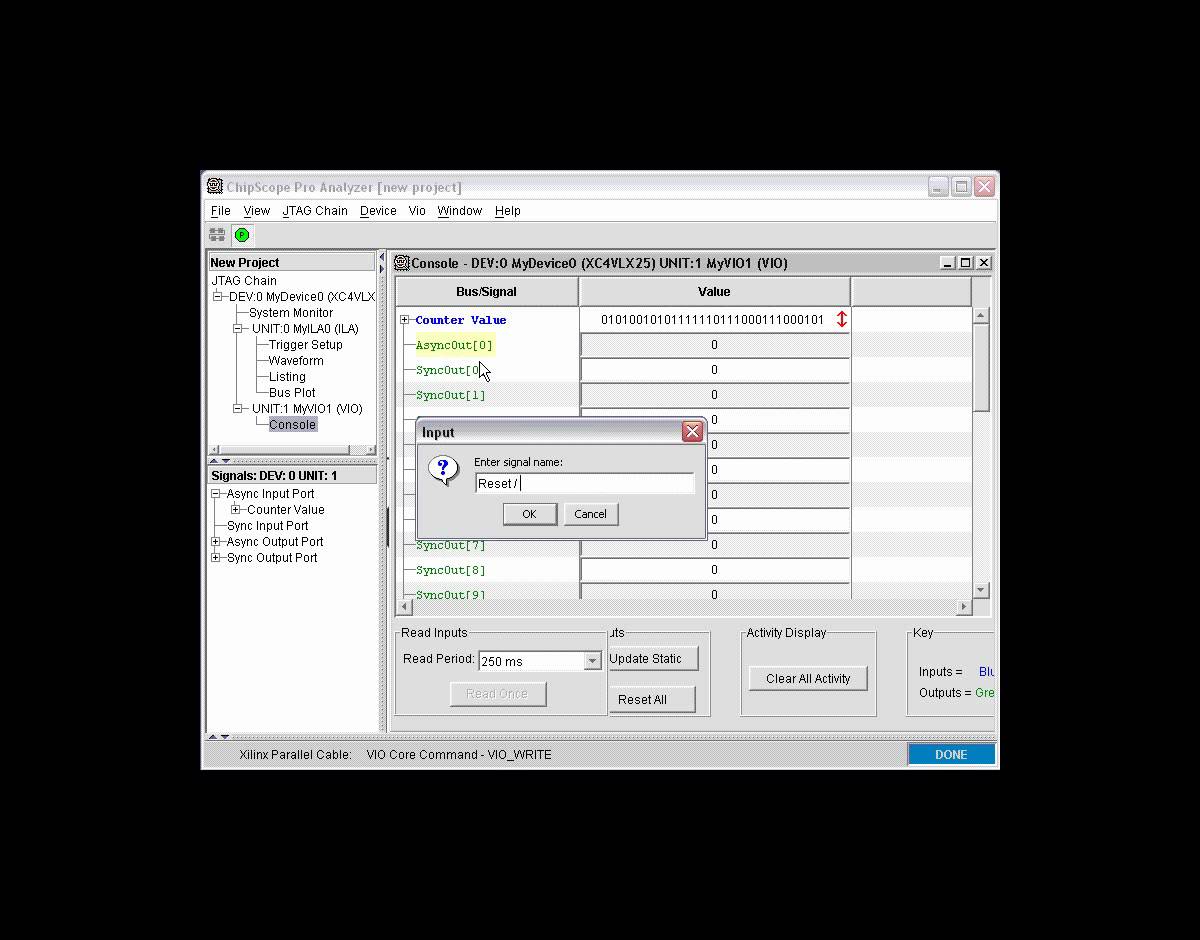

Xilinx Chipscope Pro Tutorial

By Support Team

/

This Xilinx Chipscope Pro Tutorial provides you step by step procedure to debug your FPGA Design internal signal. This procedure...

Read More

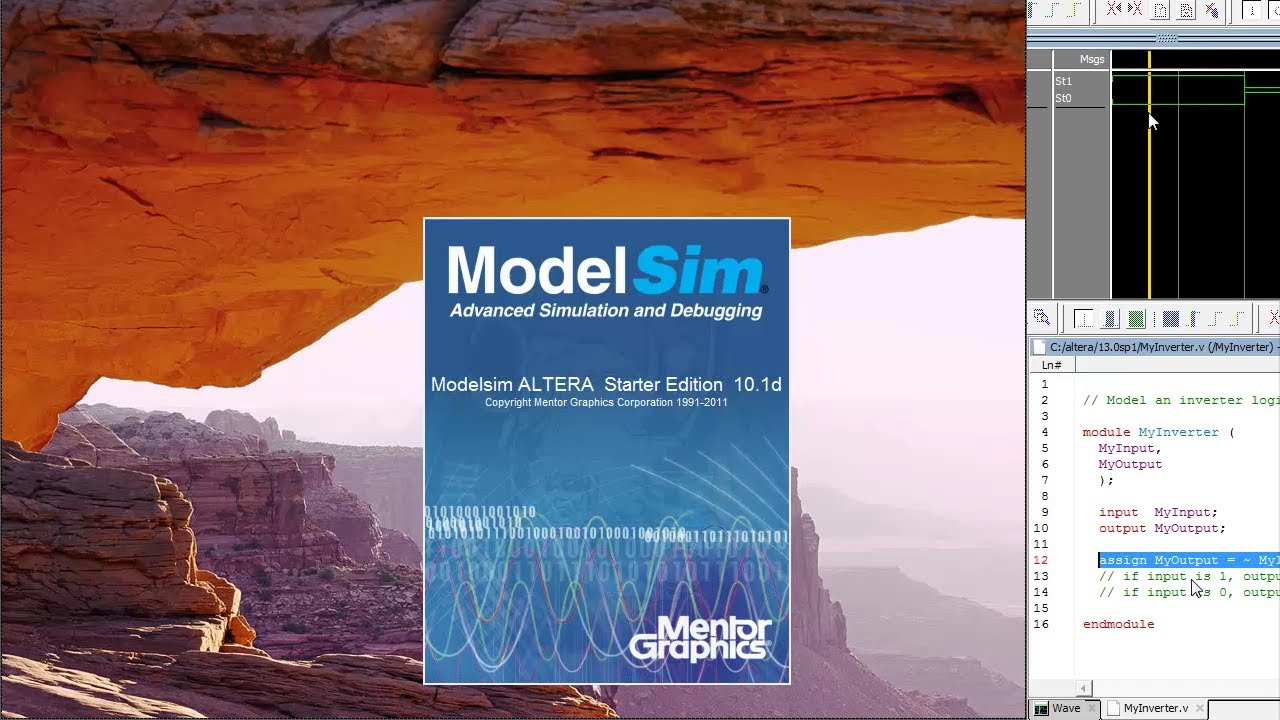

ModelSim Tutorial – Write Complie and Simulate Verilog

By Support Team

/

ModelSim Tutorial - Write Complie and Simulate Verilog

Read More

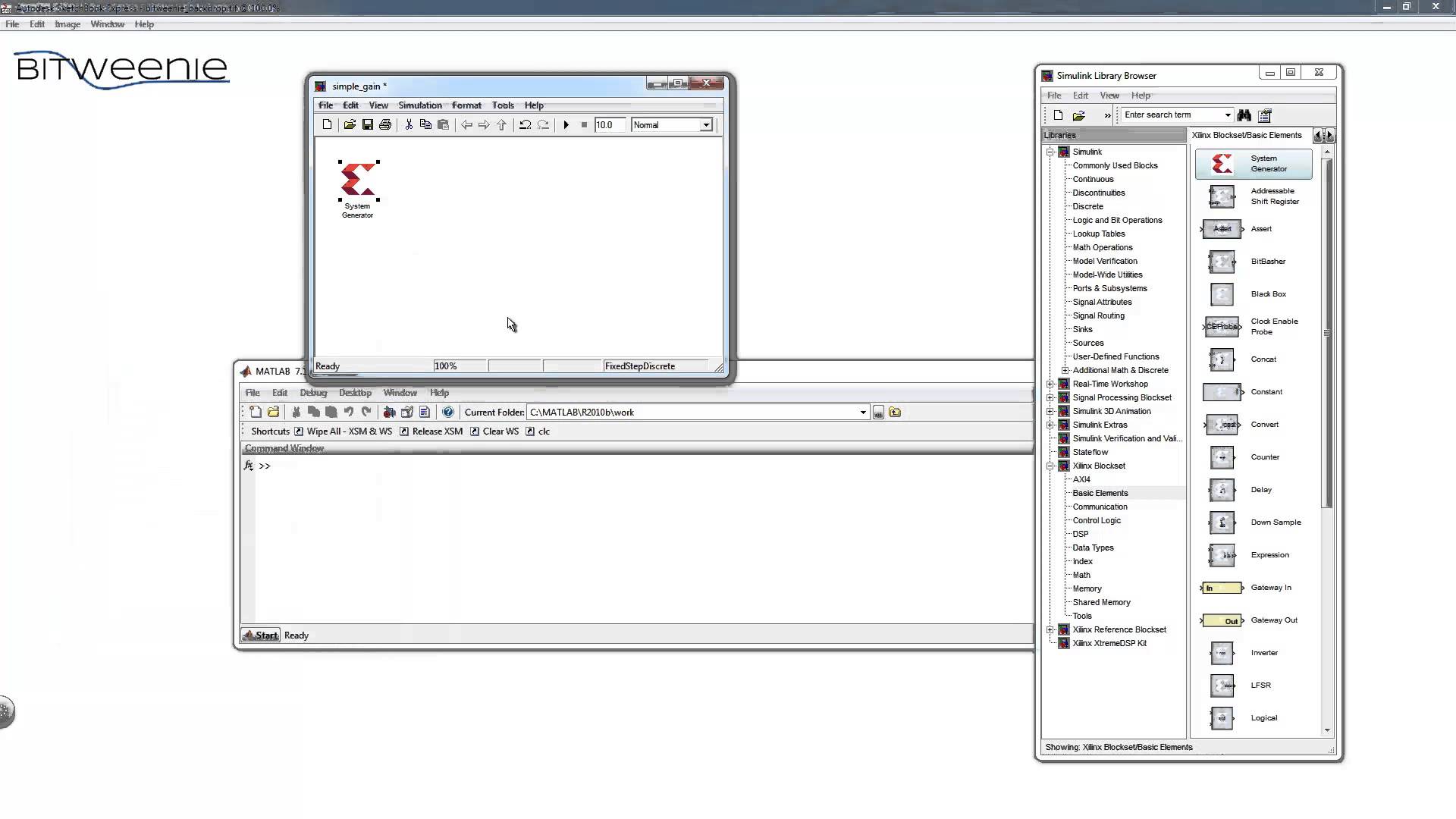

Xilinx System Generator Matlab Tutorial

By Support Team

/

This Xilinx System Generation Matlab tutorial help you to familiar with Introduction to Xilinx System generator Xilinx Toolbox in Simulink Programming...

Read More

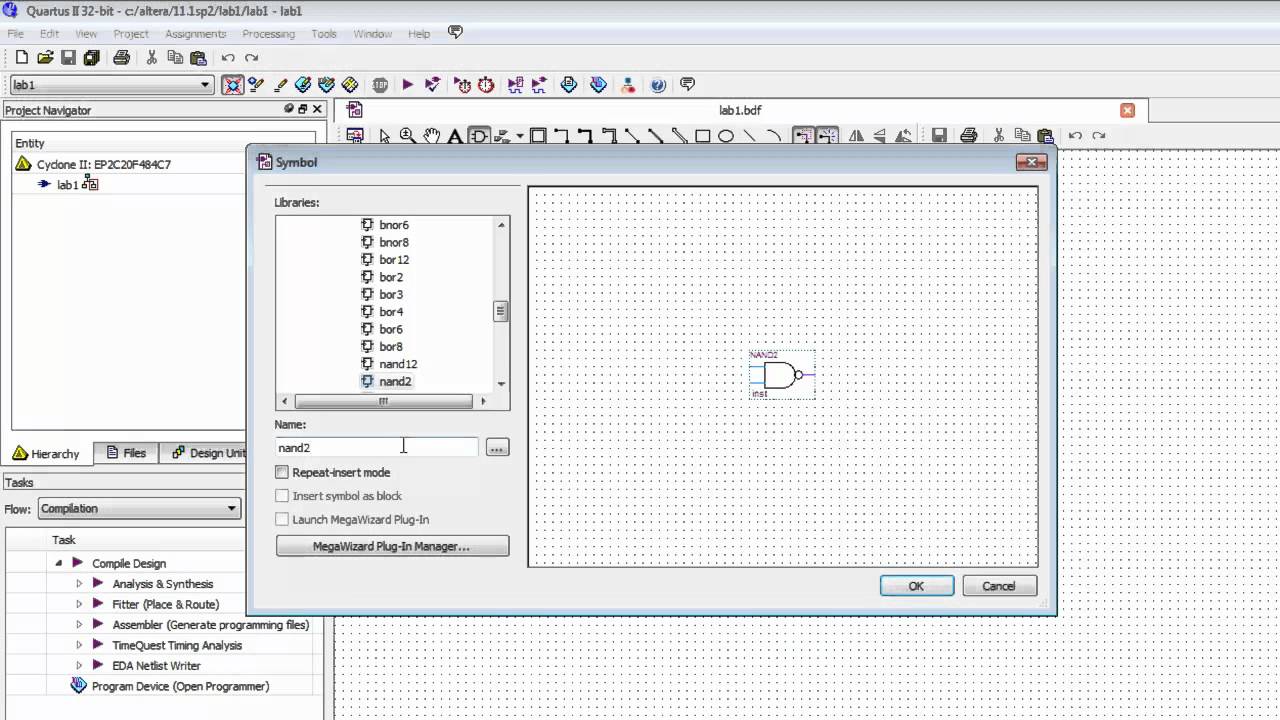

Working with Altera Quartus II Software

By Support Team

/

This Video demonstrate step by step procedure to create new Altera Quartus II Project with Schematics for NAND gate logic...

Read More

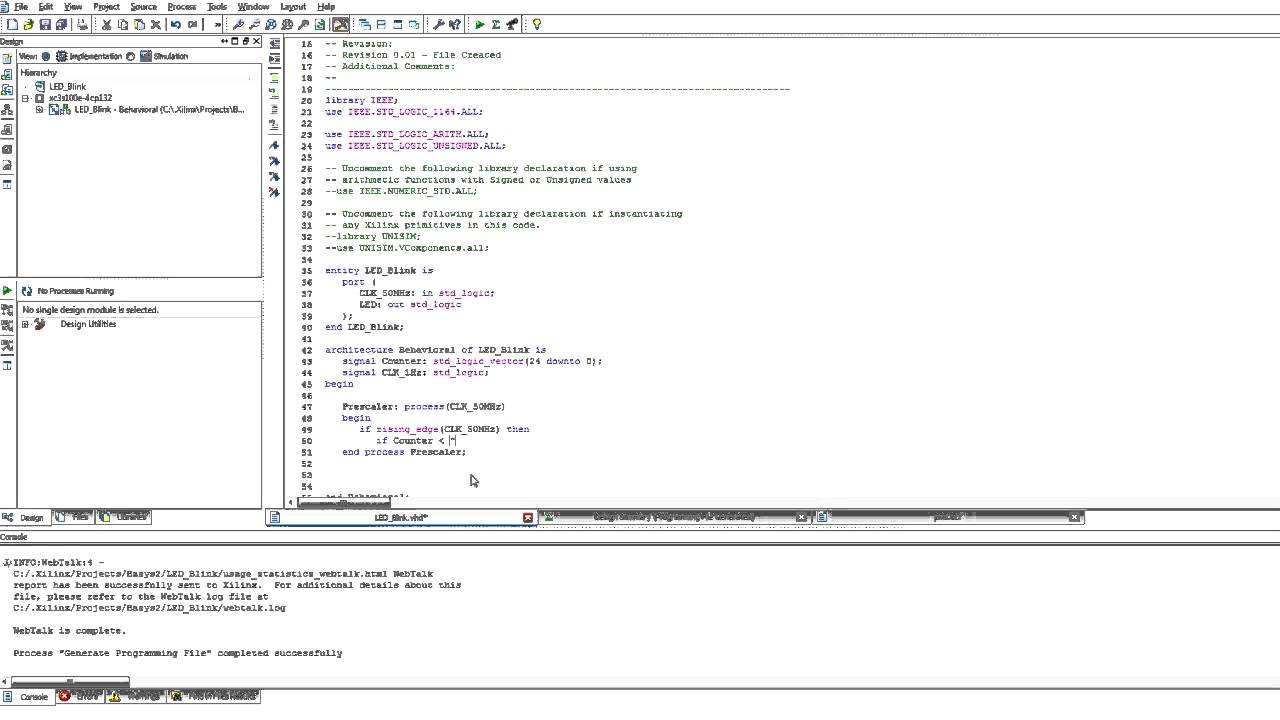

Working with Xilinx ISE Software

By Support Team

/

This Video demonstrate step by step procedure to create new Xilinx ISE Project with VHDL top module for LED Blinking...

Read More

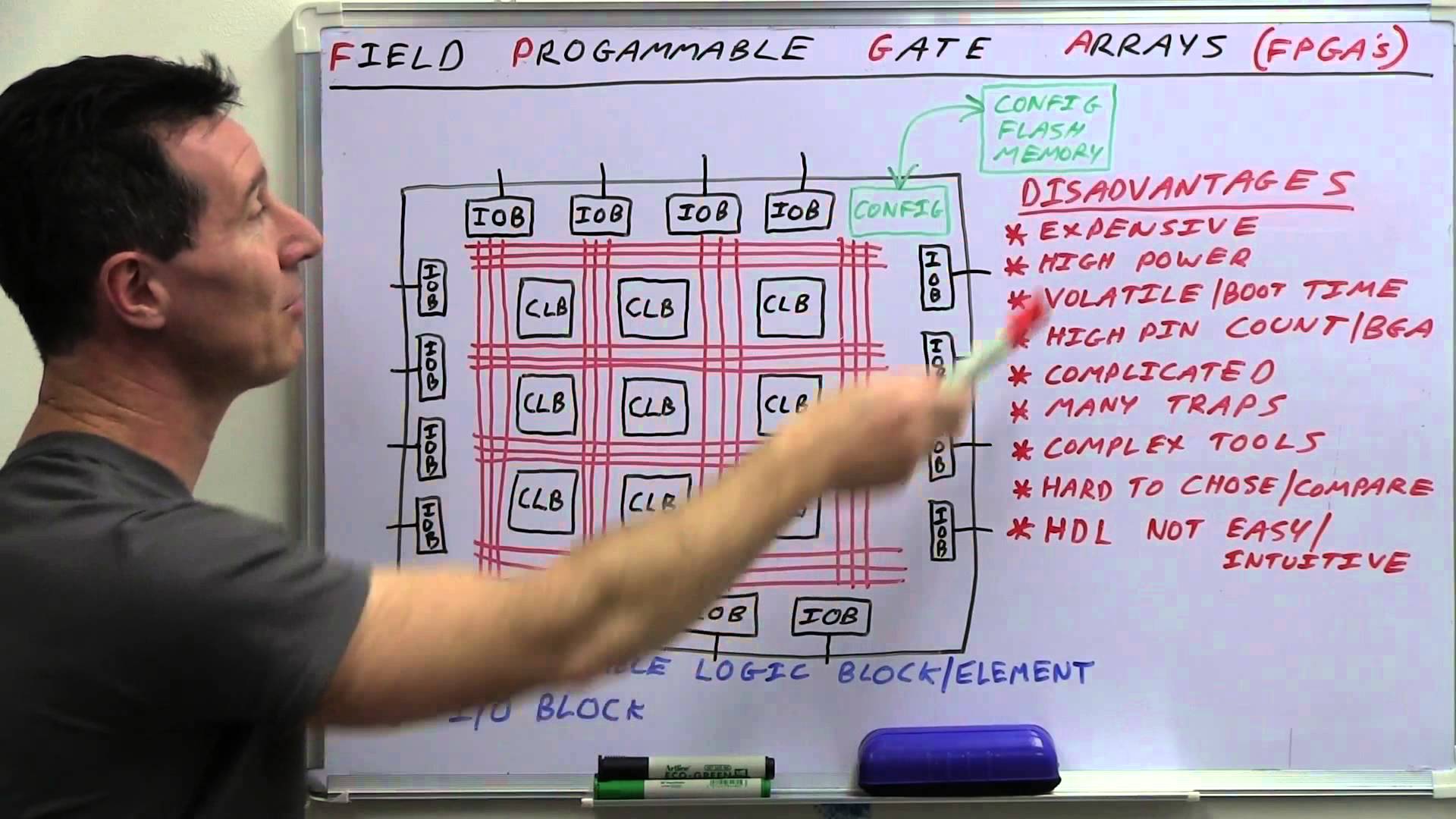

What is FPGA?

By Support Team

/

After watching this FPGA Basics video you will be able to understand what is FPGA? How to configure FPGA? Difference...

Read More

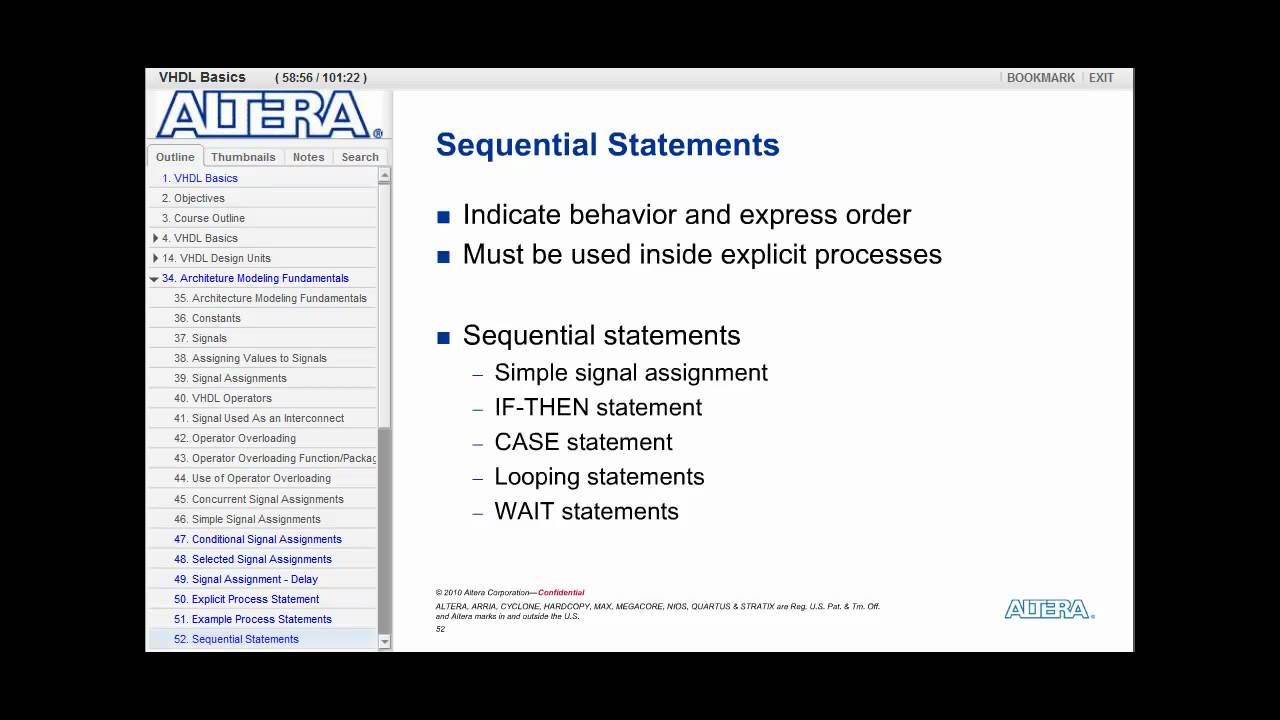

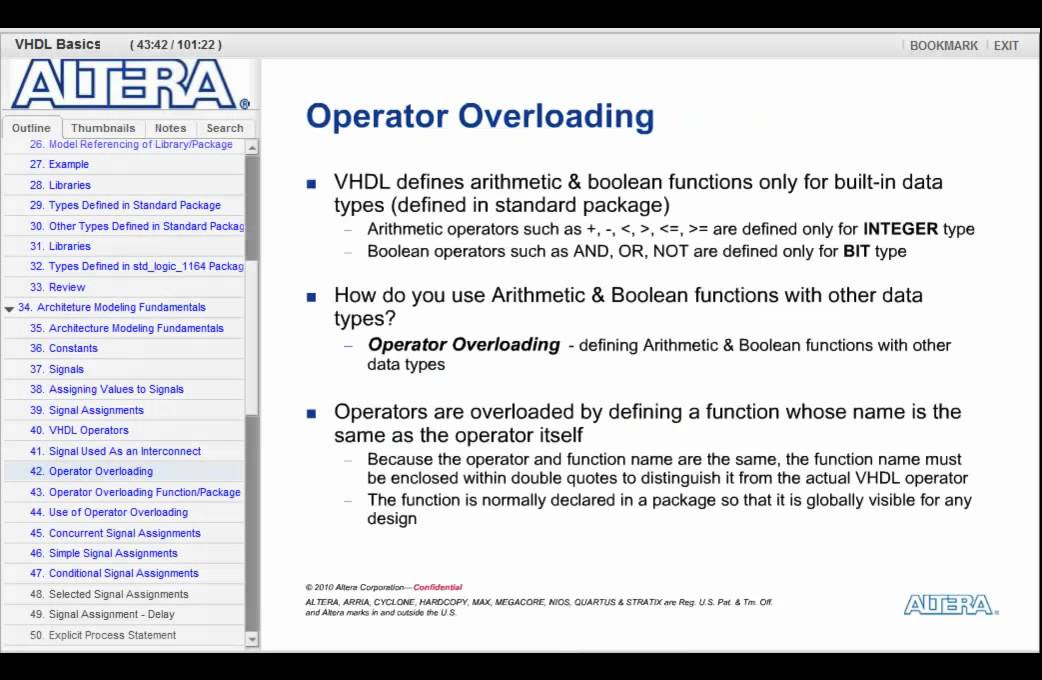

VHDL Basics Part-8

By Support Team

/

This Video tutorial introduce basic VHDL to the Beginners. Part-8

Read More

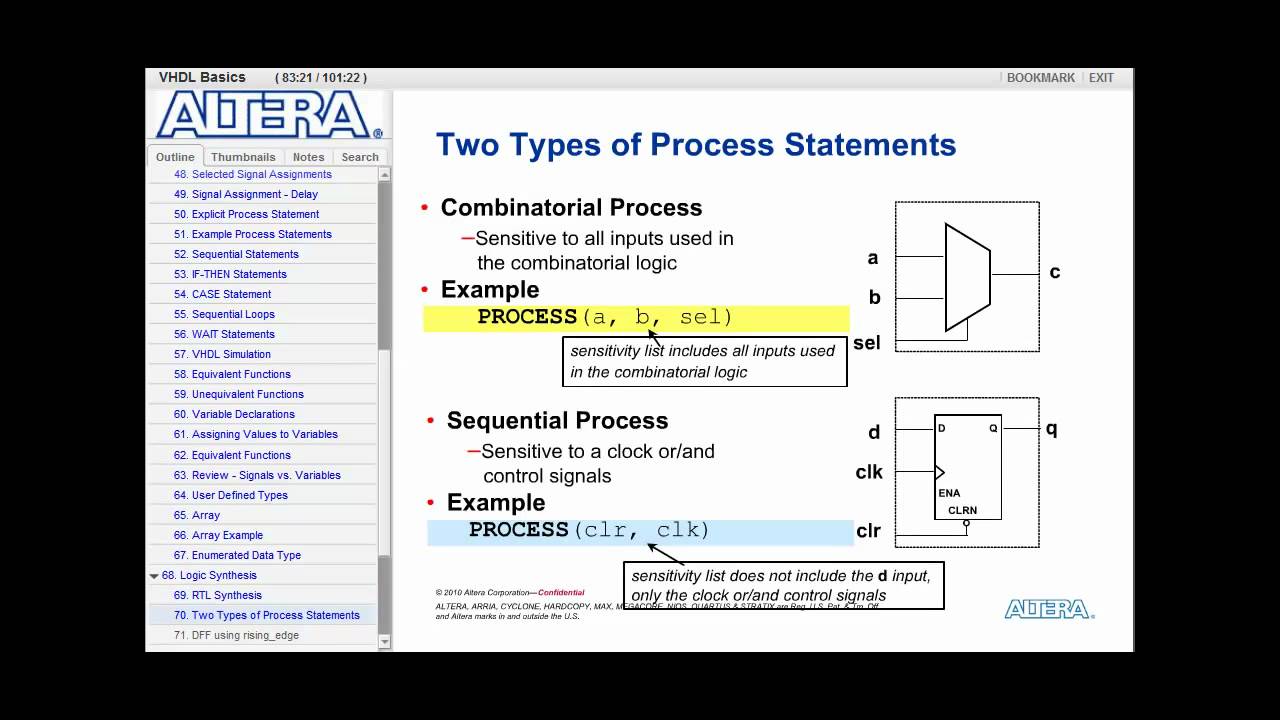

VHDL Basics Part-7

By Support Team

/

This Video tutorial introduce basic VHDL to the Beginners. Part-7

Read More

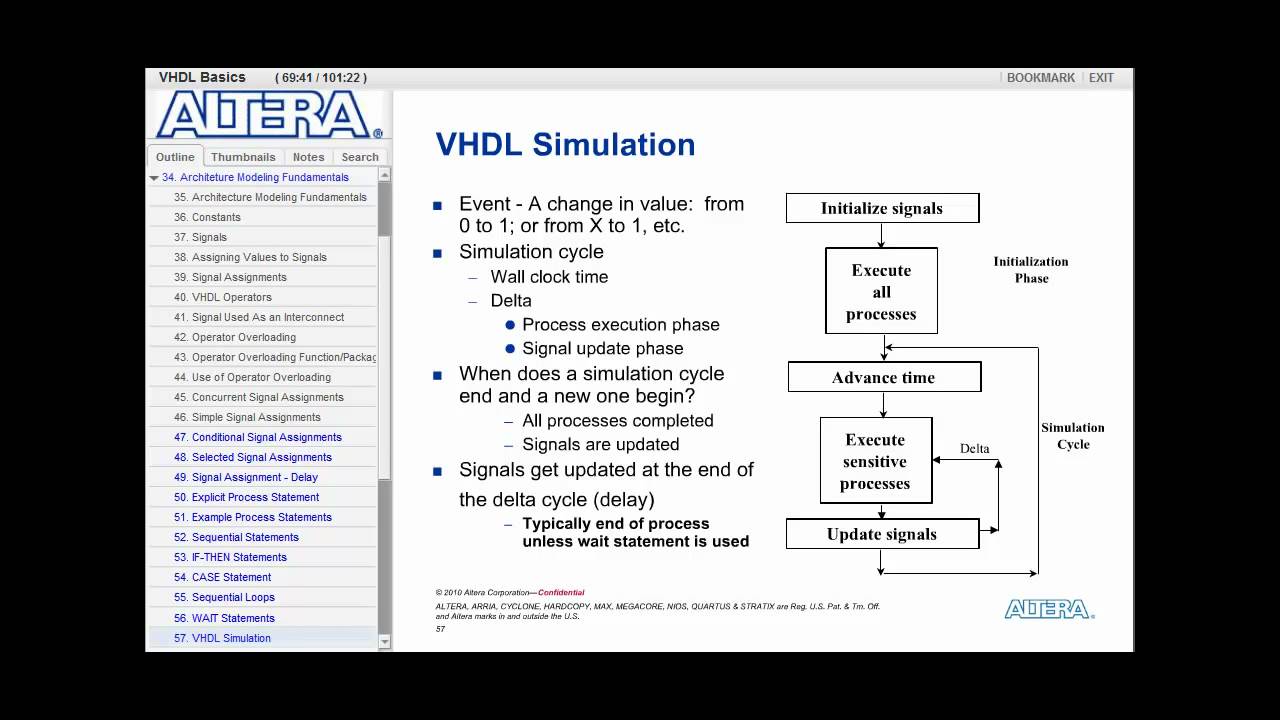

VHDL Basics Part-6

By Support Team

/

This Video tutorial introduce basic VHDL to the Beginners. Part-6

Read More

VHDL Basics Part-5

By Support Team

/

This Video tutorial introduce basic VHDL to the Beginners. Part-5

Read More

VHDL Basics Part-4

By Support Team

/

This Video tutorial introduce basic VHDL to the Beginners. Part-4

Read More

VHDL Basics Part-3

By Support Team

/

This Video tutorial introduce basic VHDL to the Beginners. Part-3

Read More

VHDL Basics Part-2

By Support Team

/

This Video tutorial introduce basic VHDL to the Beginners. Part-2

Read More

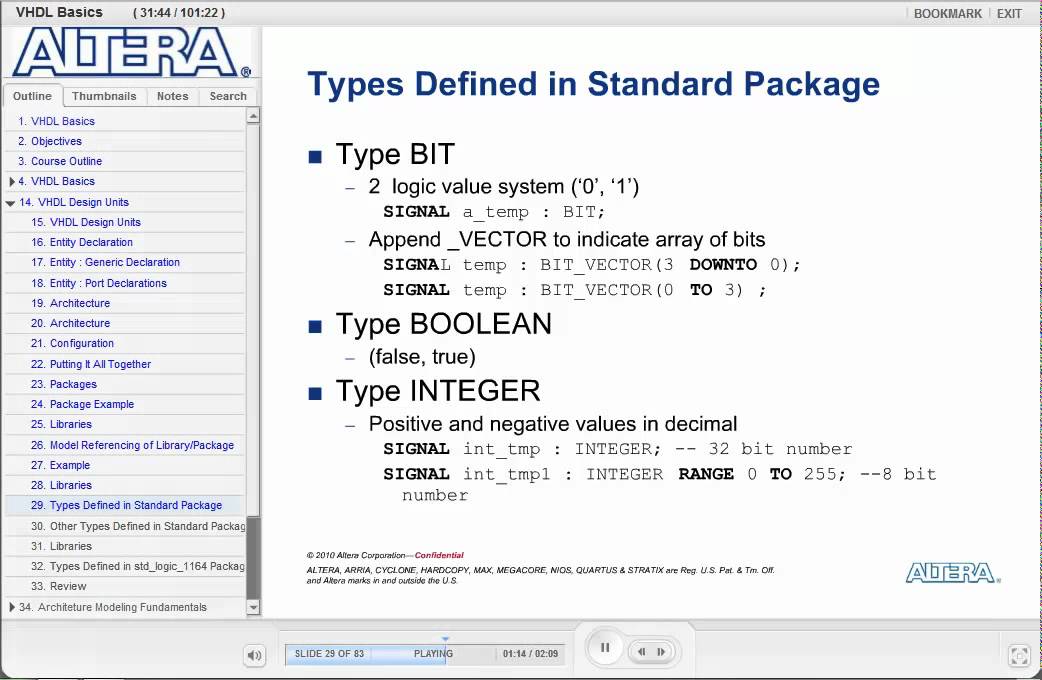

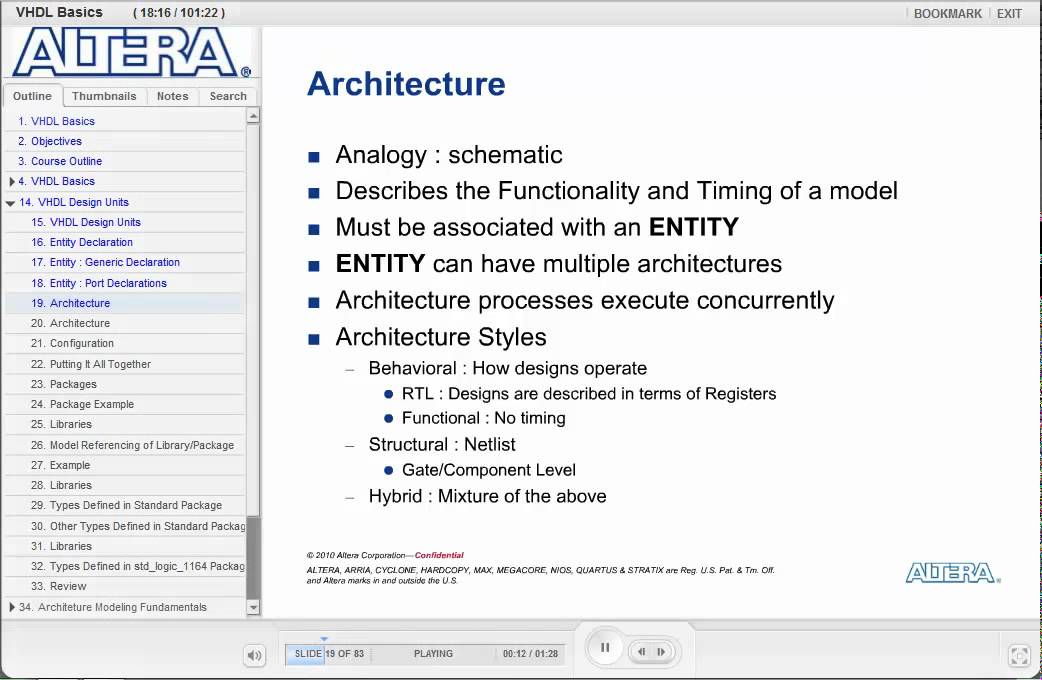

VHDL Basics Part-1

By Support Team

/

This Video tutorial introduce basic VHDL Tutorial to the Beginners. Objective of this VHDL Tutorial includes VHDL Model Construction Logic...

Read More

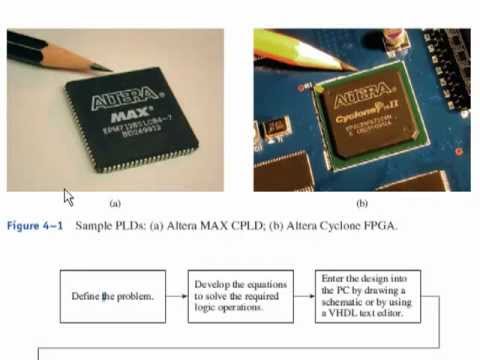

Altera FPGA Design Flow Tutorial

By Support Team

/

This tutorial video describe Altera FPGA Design flow in simple explanation. This video tutorial was originally developed by Bill Kleitz....

Read More

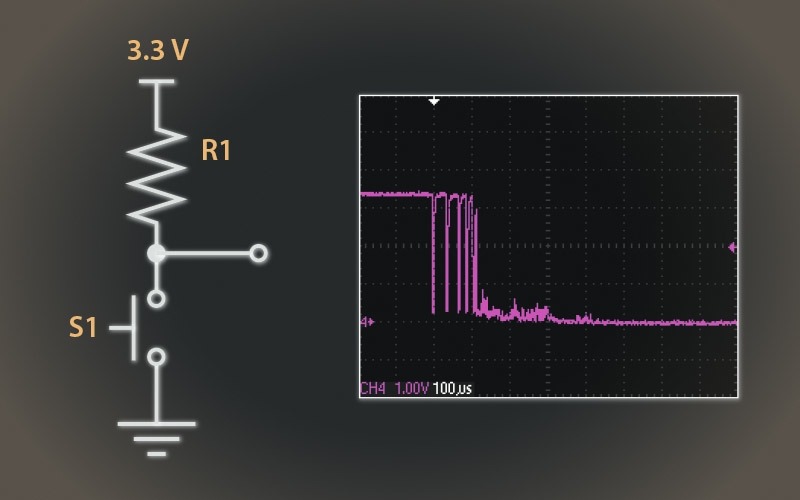

VHDL Code for Debounce Circuit in FPGA

By Support Team

/

Push Button always got the mechanical property of bouncing state at micro sec.

When you pull down the push button from high to low state. It bounce back to high and low few times before it settle at proper output. In order to avoid such bouncing state, we need to create debounce logic circuit.

Read More

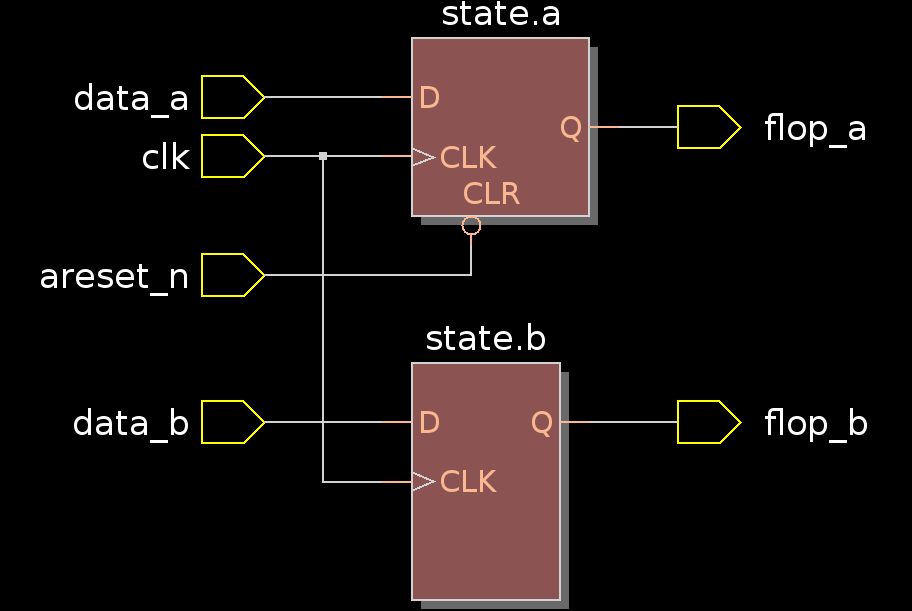

Synchronous and Asynchronous Reset VHDL

By Support Team

/

Reset Circuit helps to keep the FPGA in to Known State. There are 2 types Resets commonly employed to Reset FPGA. They are Asynchronous and Synchronous Reset.

Asynchronous Reset

Asynchronous Reset circuit is independent of free running clock. Which means Reset circuit got no knowledge of Clock input. It can assert and desert a flipflop asynchronously.

Read More

-

EDGE ZYNQ SoC FPGA Development Board₹ 17,500

EDGE ZYNQ SoC FPGA Development Board₹ 17,500 -

EDGE Artix 7 FPGA Development Board₹ 13,750

EDGE Artix 7 FPGA Development Board₹ 13,750 -

EDGE Spartan 6 FPGA Development Board₹ 8,500

EDGE Spartan 6 FPGA Development Board₹ 8,500